BS616UV2011AC-70 查看數據表(PDF) - Brilliance Semiconductor

零件编号

产品描述 (功能)

比赛名单

BS616UV2011AC-70 Datasheet PDF : 11 Pages

| |||

BSI

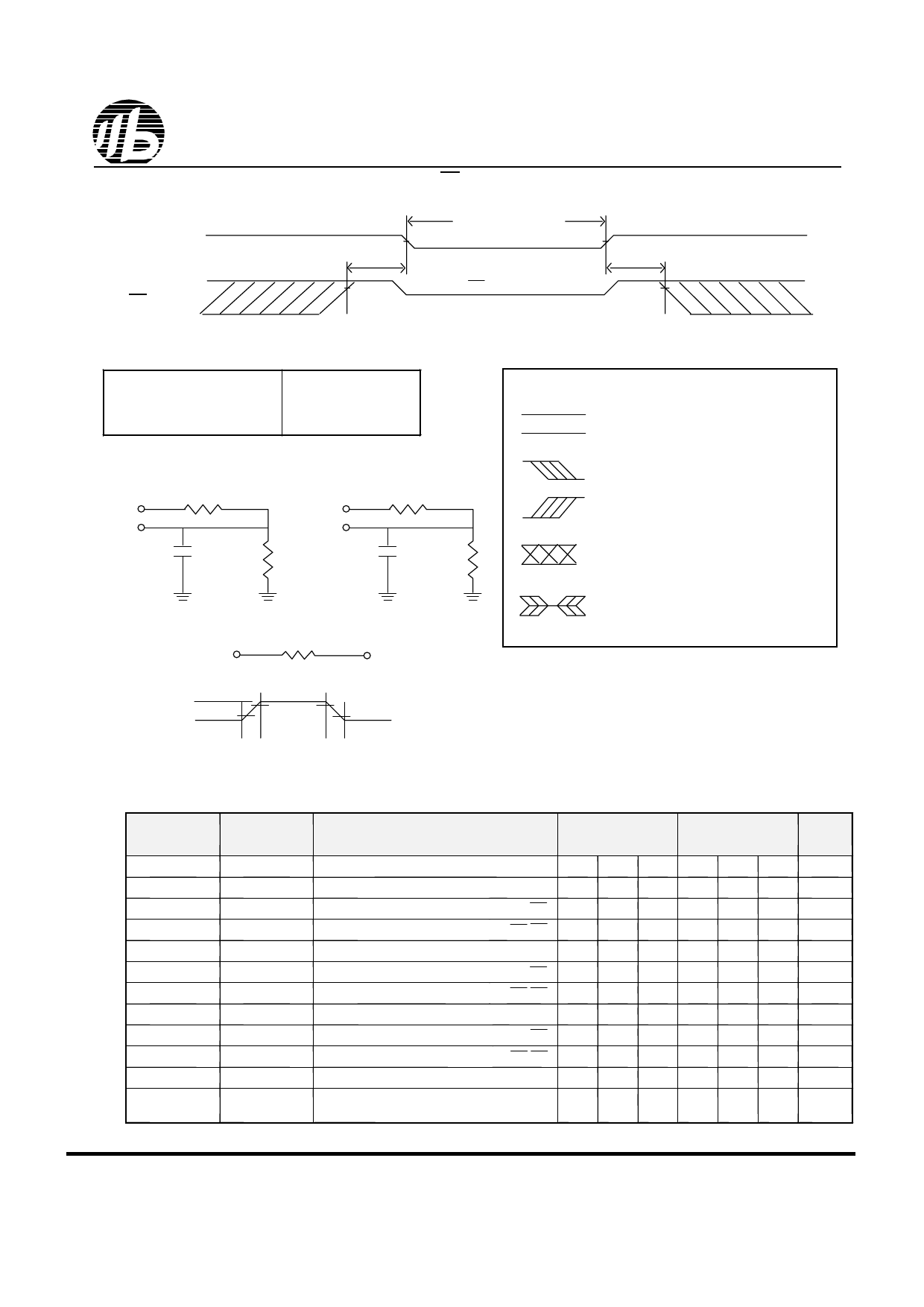

LOW VCC DATA RETENTION WAVEFORM ( CE Controlled )

Vcc

CE

Vcc

t CDR

VIH

Data Retention Mode

VDR ≥ 1.5V

CE ≥ Vcc - 0.2V

BS616UV2011

Vcc

tR

VIH

AC TEST CONDITIONS

KEY TO SWITCHING WAVEFORMS

Input Pulse Levels

Input Rise and Fall Times

Input and Output

Timing Reference Level

Vcc/0V

5ns

0.5Vcc

WAVEFORM

INPUTS

MUST BE

STEADY

OUTPUTS

MUST BE

STEADY

AC TEST LOADS AND WAVEFORMS

1333 Ω

2V

1333 Ω

2V

OUTPUT

OUTPUT

INCLUDING

JIG AND

SCOPE

100PF

2000 Ω

INCLUDING

JIG AND

SCOPE

5PF

2000 Ω

FIGURE 1A

FIGURE 1B

OUTPUT

THEVENIN EQUIVALENT

800 Ω

1.2V

MAY CHANGE

FROM H TO L

MAY CHANGE

FROM L TO H

,

DON T CARE:

ANY CHANGE

PERMITTED

DOES NOT

APPLY

WILL BE

CHANGE

FROM H TO L

WILL BE

CHANGE

FROM L TO H

CHANGE :

STATE

UNKNOWN

CENTER

LINE IS HIGH

IMPEDANCE

”OFF ”STATE

ALL INPUT PULSES

Vcc

GND

10%

→

90% 90%

←

→

FIGURE 2

10%

← 5ns

AC ELECTRICAL CHARACTERISTICS ( TA = 0 to + 70oC , Vcc = 2.0V )

READ CYCLE

JEDEC

PARAMETER

NAME

t

AVAX

t

AVQV

t

ELQV

t

BA

t

GLQV

t

ELQX

t

BE

t

GLQX

t

EHQZ

t

BDO

t

GHQZ

t

AXOX

PARAMETER

NAME

t

RC

t

AA

t

ACS

t (1)

BA

t

OE

t

CLZ

t

BE

t

OLZ

t

CHZ

t

BDO

t

OHZ

t

OH

DESCRIPTION

Read Cycle Time

Address Access Time

Chip Select Access Time

Data Byte Control Access Time

Output Enable to Output Valid

Chip Select to Output Low Z

Data Byte Control to Output Low Z

Output Enable to Output in Low Z

Chip Deselect to Output in High Z

Data Byte Control to Output High Z

Output Disable to Output in High Z

Output Disable to Address Change

(CE)

(LB,UB)

(CE)

(LB,UB)

(CE)

(LB,UB)

BS616UV2011-70

MIN. TYP. MAX.

70 --

--

-- -- 70

-- -- 70

-- -- 35

-- -- 35

10 --

--

10 --

--

10 --

--

0

-- 35

0

-- 35

0

-- 30

10 --

--

BS616UV2011-10

MIN. TYP. MAX.

100 -- --

-- -- 100

-- -- 100

-- -- 50

-- -- 50

15 -- --

15 -- --

15 -- --

0

-- 40

0

-- 40

0

-- 35

15 -- --

UNIT

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

NOTE :

1. tBA is 35ns/50ns (@speed=70ns/100ns) with address toggle. ; .tBA is 70ns/100ns (@speed=70ns/100ns) without address toggle.

R0201-BS616UV2011

4

Revision 2.5

April 2002