IDT72205LB 查看數據表(PDF) - Integrated Device Technology

零件编号

产品描述 (功能)

比赛名单

IDT72205LB

IDT72205LB Datasheet PDF : 21 Pages

| |||

IDT72205LB/72215LB/72225LB/72235LB/72245LB CMOS SyncFIFO™

256 x 18-BIT, 512 x 18, 1024 x 18, 2048 x 18 and 4096 x 18

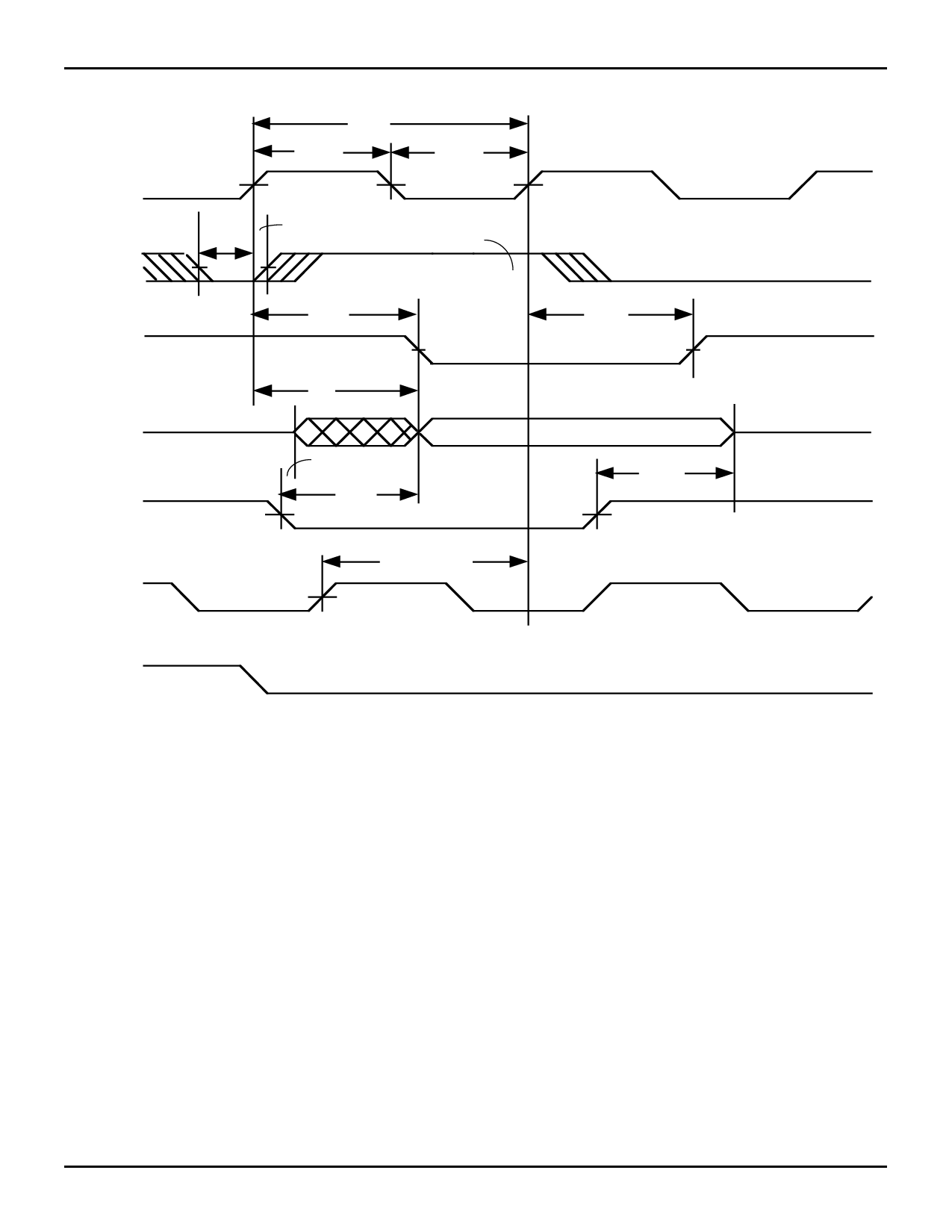

RCLK

REN

EF

Q0 - Q17

OE

WCLK

t CLKH

t CLK

t CLKL

t

ENS

tENH

NO OPERATION

tREF

tA

t OLZ

t OE

t

(1)

SKEW2

MILITARY AND COMMERCIAL TEMPERATURE RANGES

t REF

VALID DATA

t OHZ

WEN

2766 drw 09

NOTE:

1. tSKEW2 is the minimum time between a rising WCLK edge and a rising RCLK edge to guarantee that EF will go HIGH during the current clock cycle. If the

time between the rising edge of WCLK and the rising edge of RCLK is less than tSKEW2, then EF may not change state until the next RCLK edge.

Figure 7. Read Cycle Timing

5.16

11