T15N1024A 查看數據表(PDF) - Taiwan Memory Technology

零件编号

产品描述 (功能)

比赛名单

T15N1024A Datasheet PDF : 13 Pages

| |||

tm TE

CH

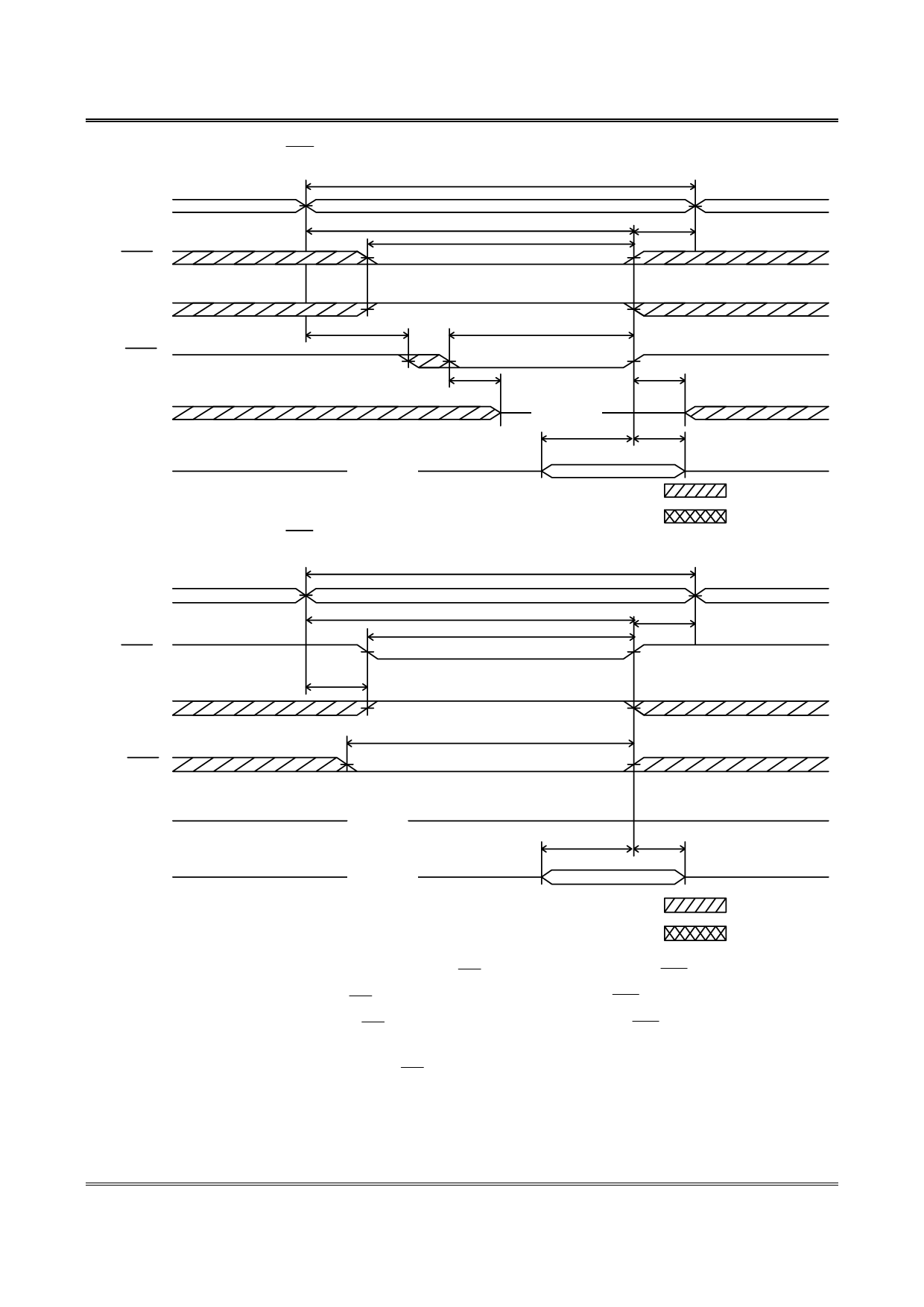

WRITE CYCLE 1

A d d re s s

CE1

( WE Controlled)

tW C

tC W

tA W

CE2

WE

D out

D IN

tA S

tW P

H ig h -Z

tW H Z

H ig h -Z

tD W

WRITE CYCLE 2

A d d re s

s

CE1

CE2

WE

( CE Controlled)

tA S

tW C

tA W

tC W

tW P

T15N1024A

tW R

tO W

tD H

D O N 'T C A R E

U N D E F IN E D

tW R

D out

H ig h -Z

tD W

tD H

D IN

H ig h -Z

D O N 'T C A R E

NOTES ( WRITE CYCLE ) :

U N D E F IN E D

1. A write occurs during the overlap of a low CE1 , a high CE2 and a low WE . A write begins at

the lateat transition among CE1 goes low, CE2 going high and WE going low. A write end at

the earliest transition among CE1 going high, CE2 going low and WE going high. tWP is

measured from the beginning of write to the end of write.

2. tCW is measured from the later of CE1 going low or CE2 going high to the end of write.

3. tAS is measured from the address valid to the beginning of write.

4. tWR is measured from the end of write to the address change.

TM Technology Inc. reserves the right

P. 8

to change products or specifications without notice.

Publication Date: FEB. 2003

Revision:E