SL74HCT373D 查看數據表(PDF) - System Logic Semiconductor

零件编号

产品描述 (功能)

比赛名单

SL74HCT373D

SL74HCT373D Datasheet PDF : 5 Pages

| |||

SL74HCT373

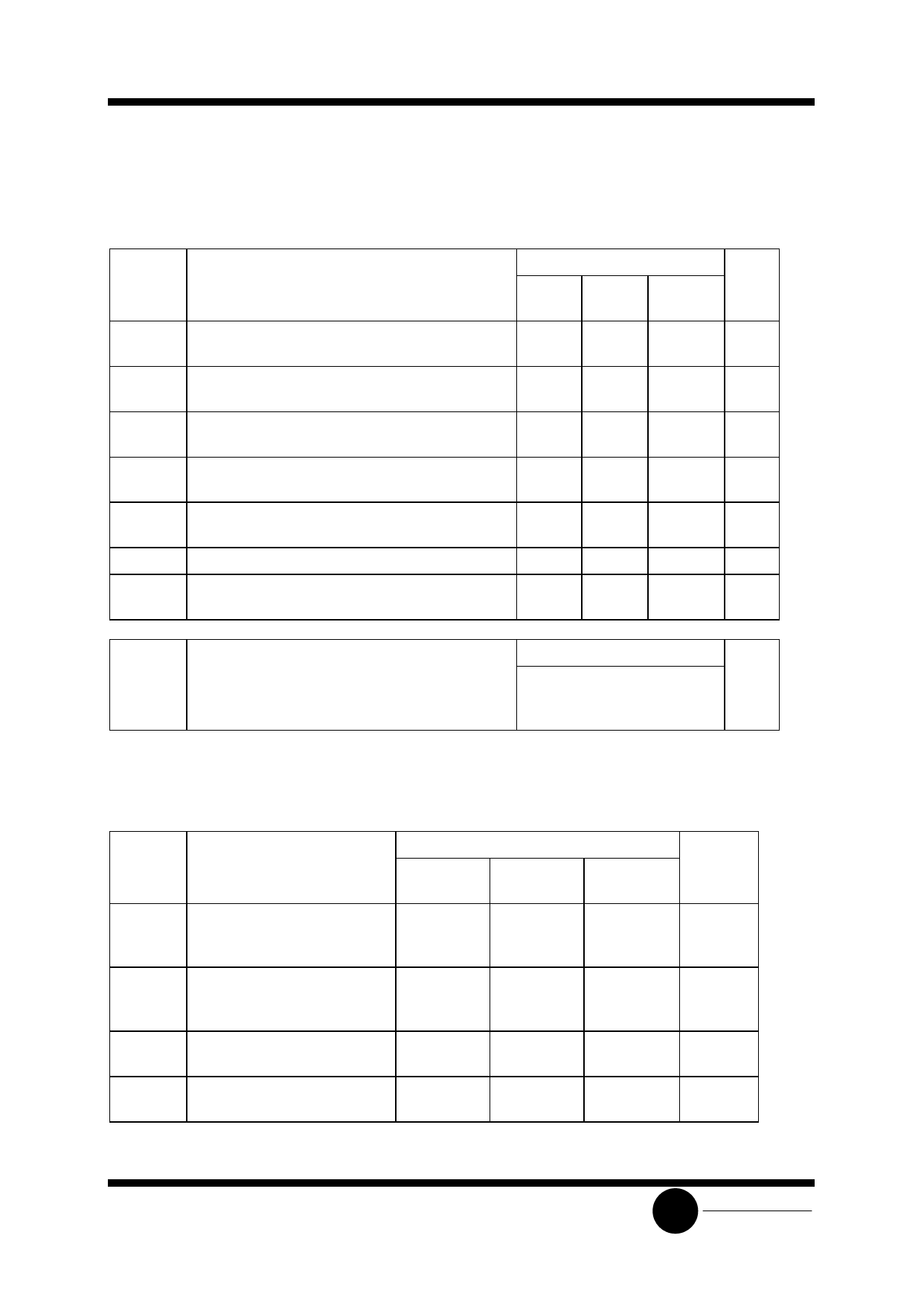

AC ELECTRICAL CHARACTERISTICS(VCC =5.0 V ± 10%, CL=50pF,Input tr=tf=6.0 ns)

Guaranteed Limit

Symbol

Parameter

25 °C to ≤85°C ≤125°C Unit

-55°C

tPLH, tPHL Maximum Propagation Delay, Input D to Q

(Figures 1 and 5)

28

35

42

ns

tPLH, tPHL Maximum Propagation Delay , Latch Enable to Q

32

40

(Figures 2 and 5)

48

ns

tPLZ, tPHZ Maximum Propagation Delay ,Output Enable to Q

30

38

(Figures 3 and 6)

45

ns

tPZL, tPZH Maximum Propagation Delay , Output Enable to Q

35

44

(Figures 3 and 6)

53

ns

tTLH, tTHL Maximum Output Transition Time, Any Output

(Figures 1 and 5)

12

15

18

ns

CIN

Maximum Input Capacitance

COUT Maximum Three-State Output Capacitance

(Output in High-Impedance State)

10

10

15

15

10

pF

15

pF

Power Dissipation Capacitance (Per Latch)

CPD Used to determine the no-load dynamic power

consumption:

PD=CPDVCC2f+ICCVCC

Typical @25°C,VCC=5.0 V

65

pF

TIMING REQUIREMENTS (VCC =5.0 V ± 10%, CL=50pF,Input t r=tf=6.0 ns)

Guaranteed Limit

Symbol

Parameter

25 °C to

-55°C

≤85°C

≤125°C

Unit

tSU

Minimum Setup Time, Input D

10

13

15

ns

to Latch Enable

(Figure 4)

th

Minimum Hold Time,Latch

10

13

15

ns

Enable to Input D

(Figure 4)

tw

Minimum Pulse Width, Latch

12

15

18

ns

Enable (Figure 2)

tr, tf Maximum Input Rise and Fall

500

500

500

ns

Times (Figure 1)

SLS

System Logic

Semiconductor