M74HC375 查看數據表(PDF) - STMicroelectronics

零件编号

产品描述 (功能)

比赛名单

M74HC375 Datasheet PDF : 10 Pages

| |||

M74HC375

QUAD D TYPE LATCH

s HIGH SPEED:

tPD = 12ns (TYP.) at VCC = 6V

s LOW POWER DISSIPATION:

ICC =2µA(MAX.) at TA=25°C

s HIGH NOISE IMMUNITY:

VNIH = VNIL = 28 % VCC (MIN.)

s SYMMETRICAL OUTPUT IMPEDANCE:

|IOH| = IOL = 4mA (MIN)

s BALANCED PROPAGATION DELAYS:

tPLH ≅ tPHL

s WIDE OPERATING VOLTAGE RANGE:

VCC (OPR) = 2V to 6V

s PIN AND FUNCTION COMPATIBLE WITH

74 SERIES 375

DESCRIPTION

The M74HC375 is an high speed CMOS QUAD

D-TYPE LATCH fabricated with silicon gate

C2MOS technology.

It contains two groups of 2 bit latches controlled by

an enable input (G1•2 or G3•4). These two latch

groups can be used in different circuits. Each latch

has Q and Q outputs (1Q - 4Q and 1Q - 4Q). The

data applied to the data input is transferred to the

Q and Q outputs when the enable input is taken

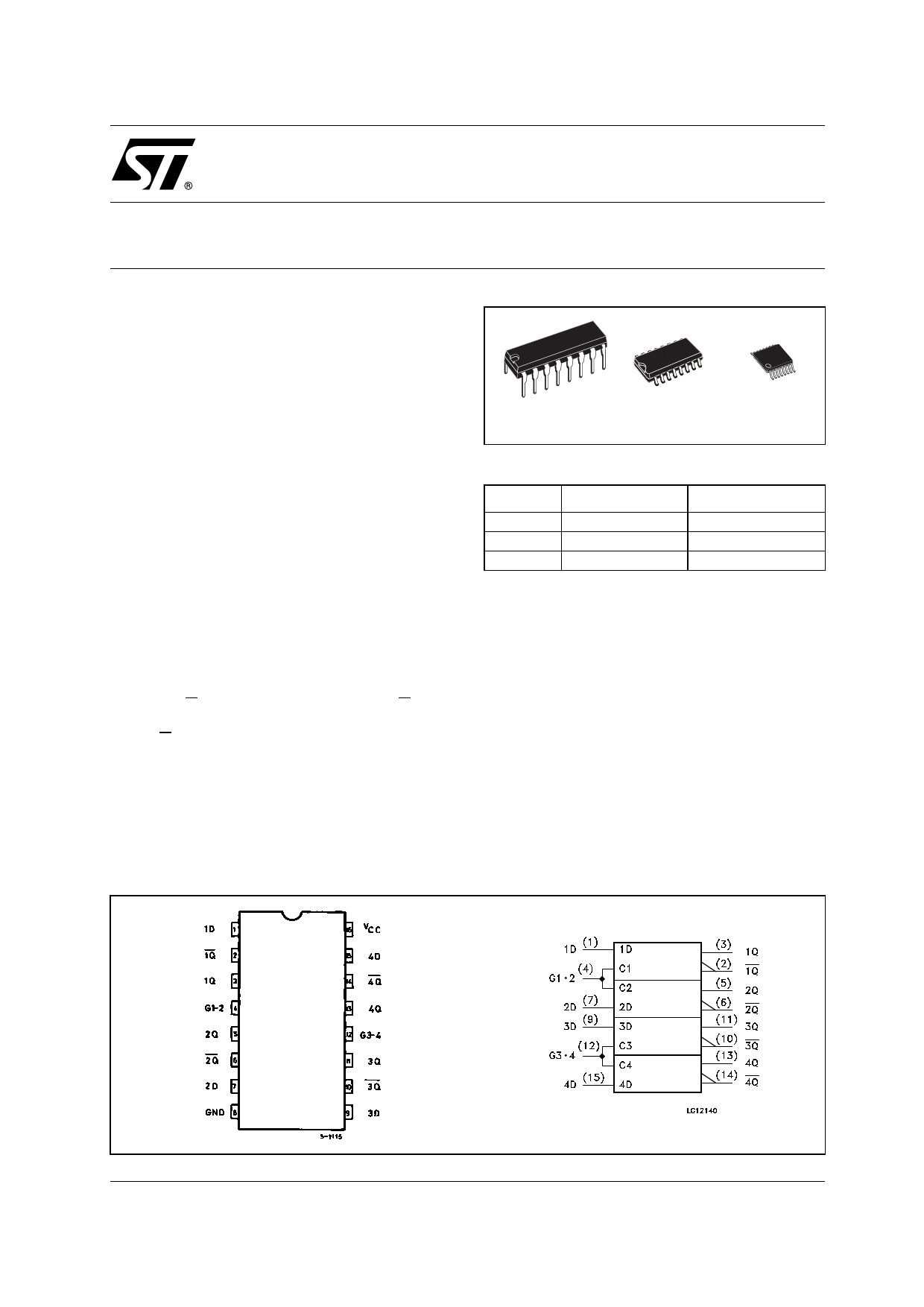

DIP

SOP

TSSOP

ORDER CODES

PACKAGE

TUBE

DIP

SOP

TSSOP

M74HC375B1R

M74HC75M1R

T&R

M74HC375RM13TR

M74HC375TTR

high and the outputs will follow the data input as

long as the enable input is kept high. When the

enable input is taken low, the information data

applied to the data input at that time is retained at

the outputs.

All inputs are equipped with protection circuits

against static discharge and transient excess

voltage.

PIN CONNECTION AND IEC LOGIC SYMBOLS

July 2001

1/10