HS-80C86RH(1995) 查看數據表(PDF) - Intersil

零件编号

产品描述 (功能)

比赛名单

HS-80C86RH Datasheet PDF : 37 Pages

| |||

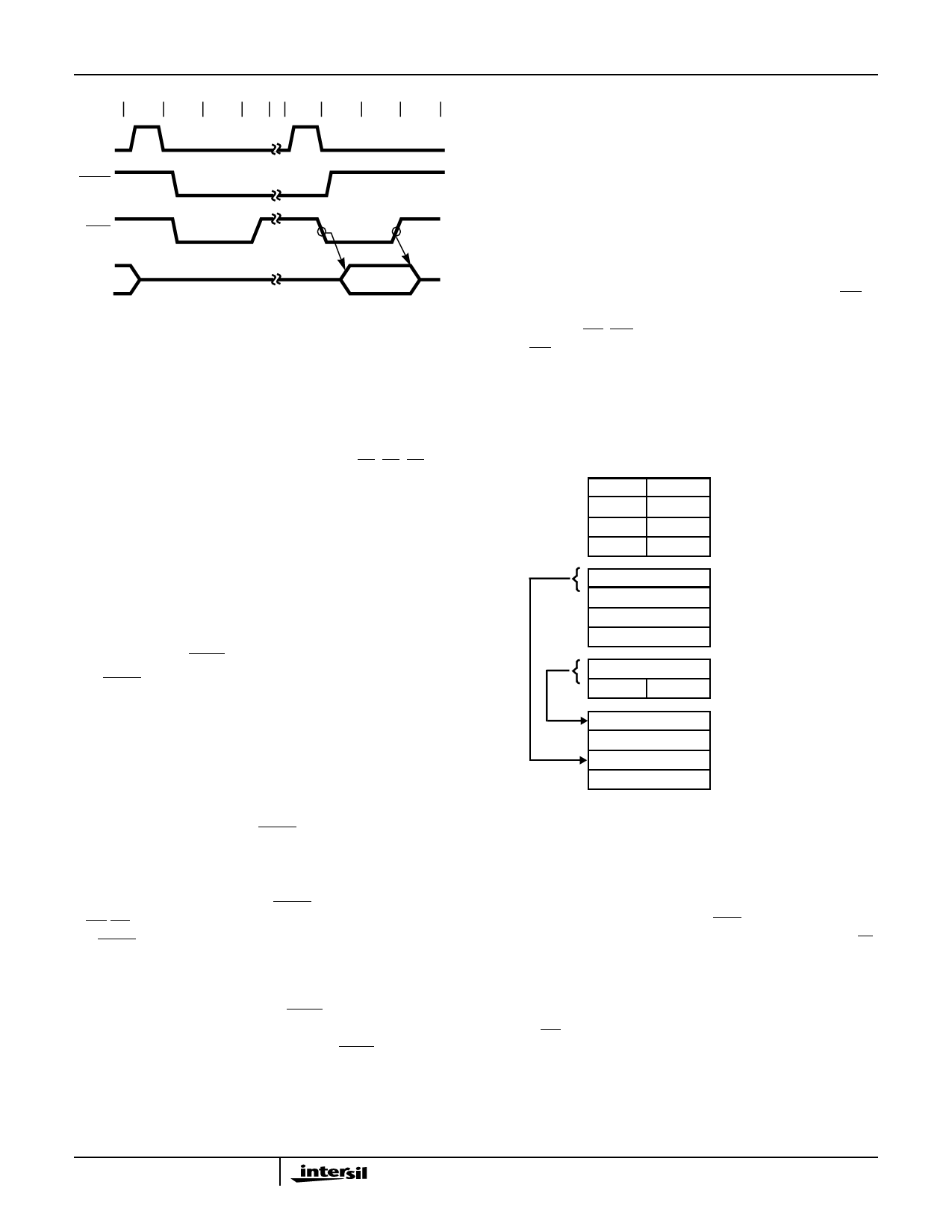

Waveforms (Continued)

CLK (HS-82C85RH OUTPUT)

TCHCTV

M/IO

TCLAV

BHE/S7, A19/S6-A16/S3

TCLLH

ALE

RDY (HS-82C85RH INPUT)

SEE NOTE 4

READY (HS-80C86RH INPUT)

HS-80C86RH

T1

T2

T3

T4

TCLCL

TCH1CH2

TCL2CL1

TW

TCHCL

TCLCH

TCLDV

TCLAX

BHE, A19-A16

TLHLL

TLLAX

S7-S3

TCHLL

VIH

TAVLL

VIL

TR1VCL

TCLRIX

TRYLCL

TCHRYX

TCHCTV

TCLAV

AD15-AD0

READ CYCLE

(NOTE 1)

(WR, INTA = VOH)

RD

DT/R

TCHCTV

DEN

TCLAZ

AD15-AD0

TAZRL

TCLRL

TCVCTV

TRYHCH

TDVCL

TCLDX1

DATA IN

TCLRH

TRHAV

TRLRH

TCVCTX

TCHCTV

FIGURE 8. BUS TIMING - MINIMUM MODE SYSTEM

NOTES:

1. All signals switch between VOH and VOL unless otherwise specified.

2. RDY is sampled near the end of T2, T3, TW to determine if TW machines states are to be inserted.

3. Two INTA cycles run back-to-back. The HS-80C86RH local ADDR/DATA bus is inactive during both INTA cycles. Control signals are

shown for the second INTA cycle.

4. Signals at HS-82C85RH are shown for reference only.

5. All timing measurements are made at 1.5V unless otherwise noted.

Spec Number 518055

876