74F543SPC 查看數據表(PDF) - Fairchild Semiconductor

零件编号

产品描述 (功能)

比赛名单

74F543SPC Datasheet PDF : 7 Pages

| |||

April 1988

Revised March 1999

74F543

Octal Registered Transceiver

General Description

The F543 octal transceiver contains two sets of D-type

latches for temporary storage of data flowing in either

direction. Separate Latch Enable and Output Enable inputs

are provided for each register to permit independent con-

trol of inputting and outputting in either direction of data

flow. The A outputs are guaranteed to sink 24 mA while the

B outputs are rated for 64 mA.

Features

s 8-bit octal transceiver

s Back-to-back registers for storage

s Separate controls for data flow in each direction

s A outputs sink 24 mA

s B outputs sink 64 mA

Ordering Code:

Order Number Package Number

Package Description

74F543SC

M24B

24-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide

74F543MSA

MSA24

24-Lead Shrink Small Outline Package (SSOP), EIAJ TYPE II, 5.3mm Wide

74F543SPC

N24C

24-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-100, 0.300 Wide

Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.

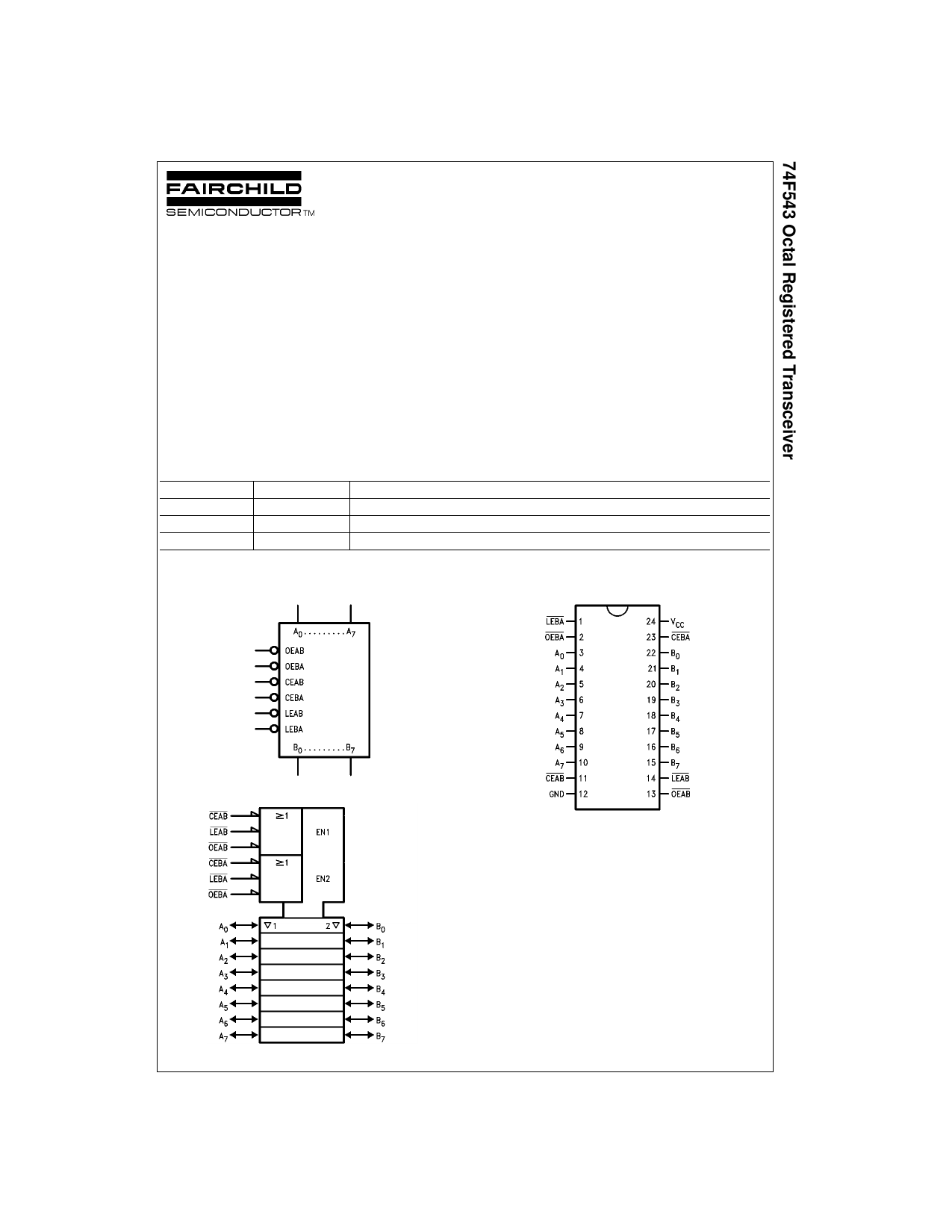

Logic Symbols

Connection Diagram

IEEE/IEC

© 1999 Fairchild Semiconductor Corporation DS009554.prf

www.fairchildsemi.com