5102ALP 查看數據表(PDF) - MAXWELL TECHNOLOGIES

零件编号

产品描述 (功能)

比赛名单

5102ALP Datasheet PDF : 14 Pages

| |||

16-Bit, 20 KHz A/D Converter

5102ALP

7. When HOLD goes low, the analog sample is captured immediately. To start conversion, HOLD must be latched by a falling

edge of CLKIN. Conversion will begin on the next rising edge of CLKIN after HOLD is latched.

8. Only valid for TRK1, TRK2 falling when SCLK is low. If SCLK is high when TRK1, TRK2 falls, then SDATA is valid tdss time after

the next falling SCLK.

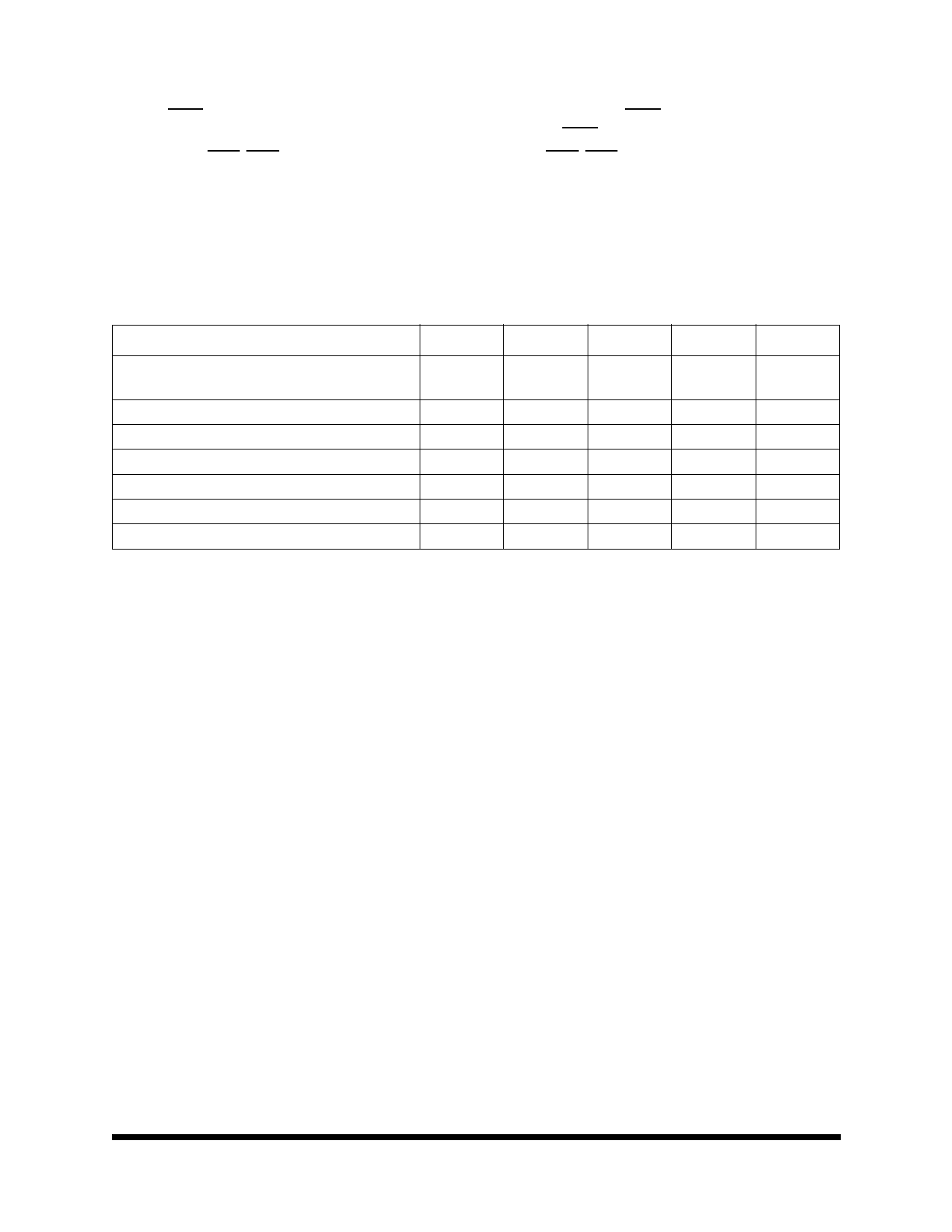

PARAMETER

TABLE 5. 5102ALP DIGITAL CHARACTERISTICS

(TA = TMIN TO TMAX; VA+, VD+ = 5V ± 10%; VA-, VD- = -5V ± 10%)

SYMBOL

MIN

TYP

MAX

UNIT

Calibration Memory Retention Power Supply Voltage

VMR

2.0

--

VA+ & VD+ 1

High-Level Input Voltage

Low-Level Input Voltage

High-Level Output Voltage 2

Low-Level Output Voltage - IOUT = 1.6 mA

Input Leakage Current

Digital Output Pin Capacitance

VIH

2.0

--

VIL

--

--

VOH

(VD+) -1.0

--

VOL

--

--

IIN

--

--

COUT

--

9

--

V

--

V

0.8

V

--

V

0.4

V

10

µA

--

pF

1. VA- and VD- can be any value from zero to -5V for memory retention. Neither VA- or VD- should be allowed to go positive.

AIN1, AIN2 or VREF must not be greater than VA+ or VD+. This parameter is guaranteed by characterization.

2. IOUT = -100 µ A. This specification guarantees TTL compatibility (VOH = 2.4V @ IOUT = -40 µ A.

LPT™ OPERATION

Latchup Protection Technology (LPT™) automatically detects an increase in the supply current of the 5102ALP con-

verter due to a single event effect and internally cycle the power to the converter off, then on, which restores the

steady state operation of the device.

If data outputs are connected to a bus with other bus driver circuits, all external data bus drivers must be tri-stated and

individual pull up resistors to the supply voltage (if used on the data bus) must no be less than 10 K ohm typical to

assure proper single event effect recovery.

STATUS can also be used to generate an input to the system data processor indicating that an LPT™ cycle has

occurred, and the protected device output accuracy may not be met until after the respective recovery time to the

event. The STATUS signal is generated from an advanced CMOS logic gate output. This output may not exhibit a

monotonic fall time and may even oscillate briefly while power is being restored to the protected device and the decou-

pling capacitance is charged. Loading on the STATUS output should be minimized because this signal is used inter-

nally by the 5102ALP. It is recommended that load current not exceed 2 mA and load capacitance be kept will below

1000 pF.

01.17.05 REV 3 All data sheets are subject to change without notice 6

©2005 Maxwell Technologies Inc.

All rights reserved.