EDS2504APTA-TI 查看數據表(PDF) - Elpida Memory, Inc

零件编号

产品描述 (功能)

比赛名单

EDS2504APTA-TI Datasheet PDF : 51 Pages

| |||

EDS2504APTA/08APTA/16APTA-TI

Test Conditions

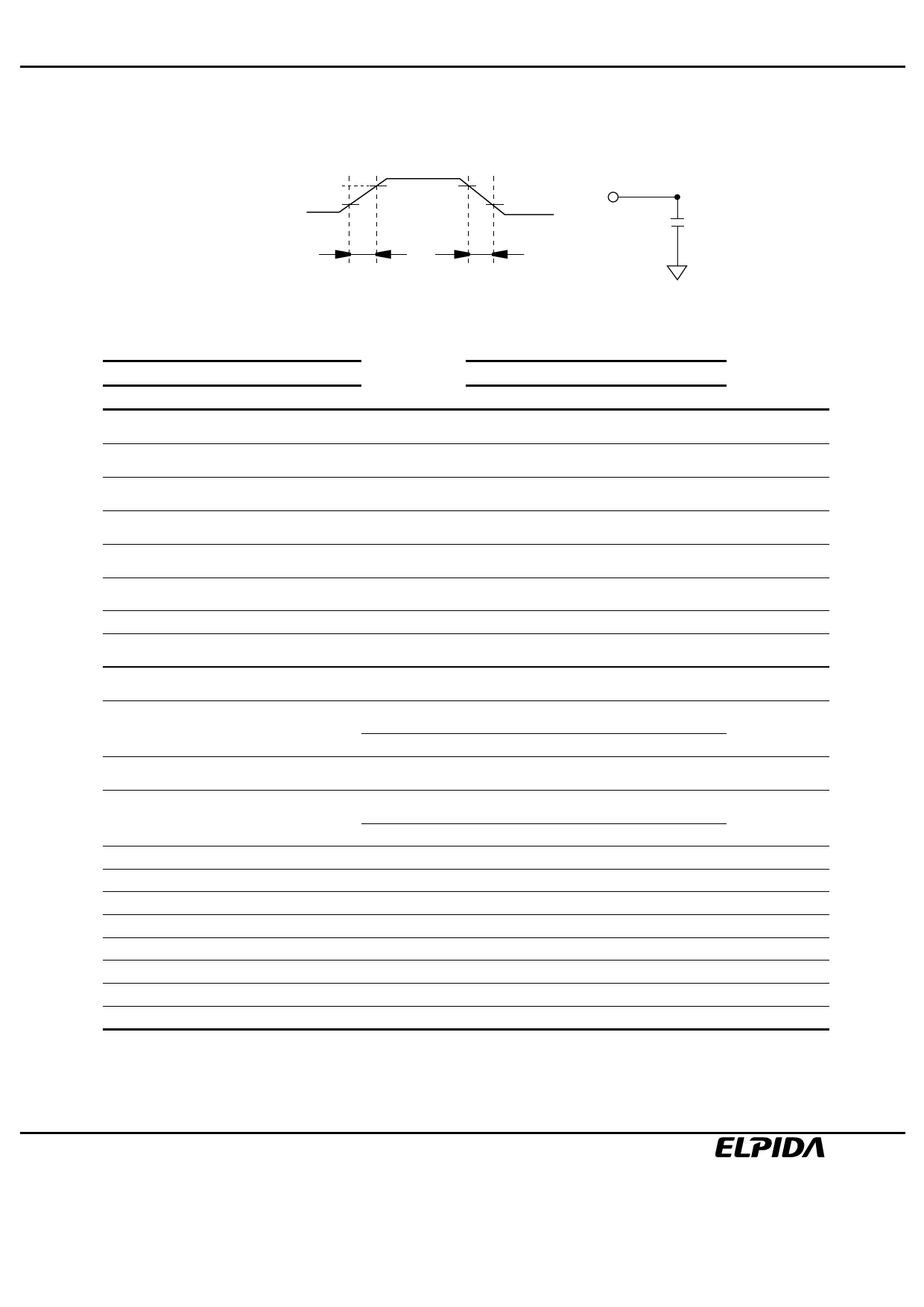

• Input and output timing reference levels: 1.4V

• Input waveform and output load: See following figures

2.4 V

input

2.0 V

I/O

0.4 V 0.8 V

tT

tT

Output load

Relationship Between Frequency and Minimum Latency

Parameter

-7A

-75

Frequency (MHz)

133

tCK (ns)

Symbol

7.5

7.5

Active command to column command

(same bank)

lRCD

2

3

Active command to active command

(same bank)

lRC

8

9

Active command to precharge command

(same bank)

lRAS

6

6

Precharge command to active command

(same bank)

lRP

2

3

Write recovery or data-in to precharge

command (same bank)

lDPL

2

2

Active command to active command

(different bank)

lRRD

2

2

Self refresh exit time

lSREX

1

1

Last data in to active command

(Auto precharge, same bank)

lDAL

4

5

Self refresh exit to command input

lSEC

8

9

Precharge command to high impedance

(CL = 2)

lHZP

2

2

(CL = 3)

lHZP

3

3

Last data out to active command

(auto precharge) (same bank)

lAPR

1

1

Last data out to precharge (early precharge)

(CL = 2)

lEP

–1

–1

(CL = 3)

lEP

–2

–2

Column command to column command

lCCD

1

1

Write command to data in latency

lWCD

0

0

DQM to data in

DQM to data out

lDID

0

0

lDOD

2

2

CKE to CLK disable

lCLE

1

1

Register set to active command

lMRD

2

2

/CS to command disable

lCDD

0

0

Power down exit to command input

lPEC

1

1

Notes: 1.IRCD to IRRD are recommended value.

2. Be valid [DESL] or [NOP] at next command of self refresh exit.

3. Except [DESL] and [NOP]

CL

Notes

1

1

1

1

1

1

2

= [lDPL + lRP]

= [lRC]

3

Preliminary Data Sheet E0248E10 (Ver. 1.0)

7