G690L293T96 查看數據表(PDF) - Global Mixed-mode Technology Inc

零件编号

产品描述 (功能)

比赛名单

G690L293T96 Datasheet PDF : 13 Pages

| |||

Global Mixed-mode Technology Inc.

G690/G691

Pin Description

PIN

NAME

1

GND

2

(G691L/G690L)

RESET

(G690H)

3

VCC

Ground

FUNCTION

RESET Output remains low while VCC is below the reset threshold, and for at least 140ms after

VCC rises above the reset threshold.

RESET Output remains high while VCC is below the reset threshold, and for at least 140ms after

VCC rises above the reset threshold.

Supply Voltage (+5V, +3.3V, +3.0V)

Detailed Description

A microprocessor’s (µP’s) reset input starts the µP in a

known state. The G691L/G690L/G690H assert reset to

prevent code-execution errors during power-up,

power-down, or brownout conditions. They assert a

reset signal whenever the VCC supply voltage declines

below a preset threshold, keeping it asserted for at

least 140ms after VCC has risen above the reset

threshold. The G691L uses an open-drain output, and

the G690L/G690H have a push-pull output stage.

Connect a pull-up resistor on the G691L’s RESET out-

put to any supply between 0 and 5.5V.

600

500

400

300

200

G69_ _ 463/438/400

100

G69_ _ 308/293/263

0

1

10

100

1000

Reset Comparator Overdrive, VTH- VCC (mV)

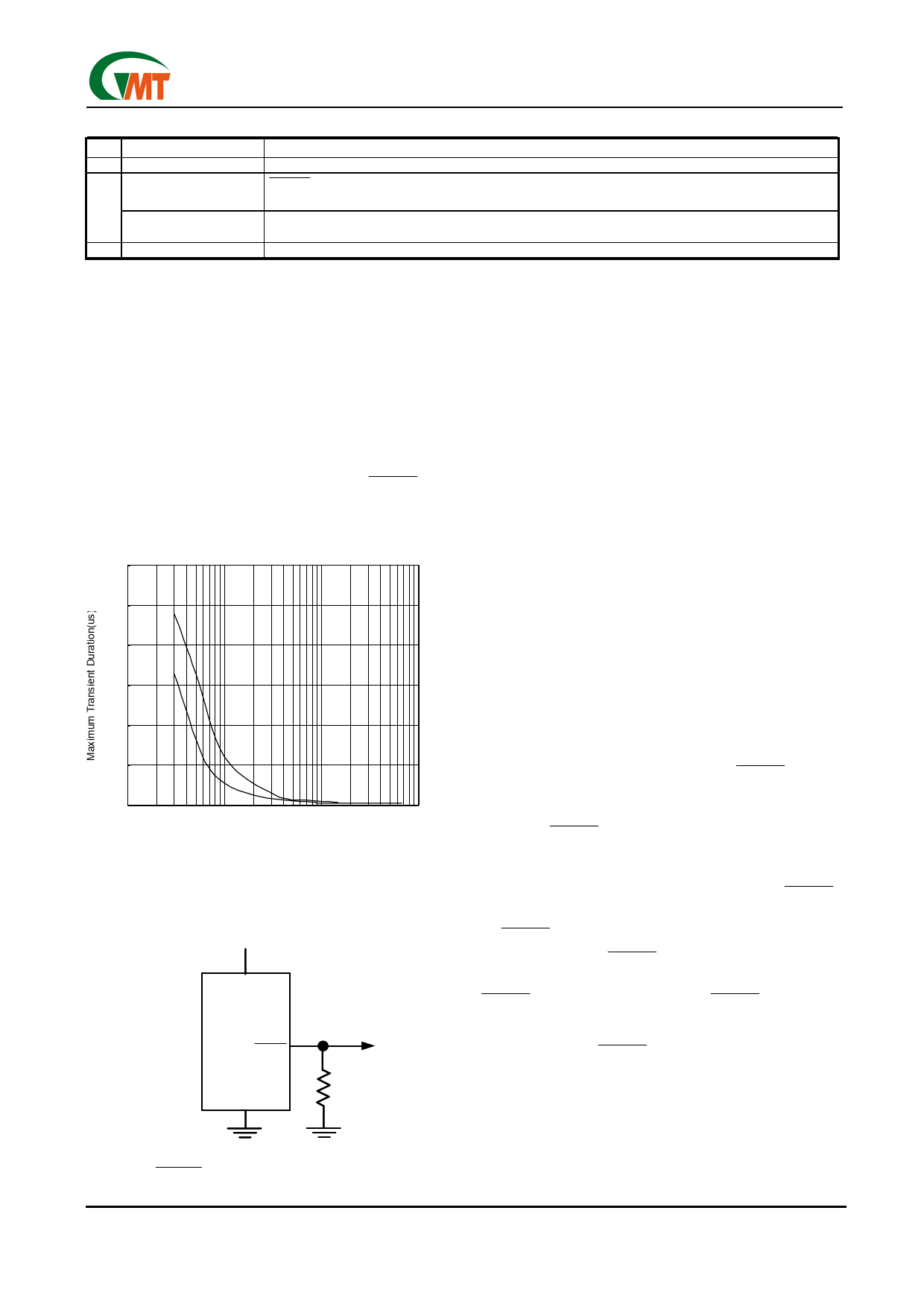

Figure 1. Maximum Transient Duration Without

Causing a Reset Pulse vs. Reset Com-

parator Overdrive

VCC

G690

RESET

GND

R1

100k

Applications Information

Negative-Going VCC Transients

In addition to issuing a reset to the µP during

power-up, power-down, and brownout conditions, the

G691L/G690H/G690L are relatively immune to short-

duration negative-going VCC transients (glitches).

Figure 1 shows typical transient duration vs. reset

comparator overdrive, for which the G691L/G690H/

G690L do not generate a reset pulse. The graph was

generated using a negative-going pulse applied to VCC,

starting 0.5V above the actual reset threshold and

ending below it by the magnitude indicated (reset

comparator overdrive). The graph indicates the maxi-

mum pulse width a negative-going VCC transient can

have without causing a reset pulse. As the magnitude

of the transient increases (goes farther below the reset

threshold), the maximum allowable pulse width de-

creases. Typically, for the G69_ _463 and G69_ _438,

a VCC transient that goes 100mV below the reset

threshold and lasts 7µs or less will not cause a reset

pulse. A 0.1µF bypass capacitor mounted as close as

possible to the VCC pin provides additional transient

immunity.

Ensuring a Valid Reset Output Down to VCC = 0

When VCC falls below 1V, the G690 RESET output

no longer sinks current—it becomes an open circuit.

Therefore, high-impedance CMOS logic inputs con-

nected to RESET can drift to undetermined voltages.

This presents no problem in most applications since

most µP and other circuitry is inoperative with VCC

below 1V. However, in applications where RESET

must be valid down to 0V, adding a pull-down resistor

to RESET causes any stray leakage currents to flow

to ground, holding RESET low (Figure 2). R1’s value

is not critical; 100kΩ is large enough not to load

RESET and small enough to pull RESET to ground.

A 100kΩ pull-up resistor to VCC is also recommended

for the G691L if RESET is required to remain valid

for VCC < 1V.

Figure2. RESET Valid to VCC = Ground Circuit

Ver: 1.3

Oct 31, 2002

8

TEL: 886-3-5788833

http://www.gmt.com.tw