HI5828(1999) 查看數據表(PDF) - Intersil

零件编号

产品描述 (功能)

比赛名单

HI5828 Datasheet PDF : 12 Pages

| |||

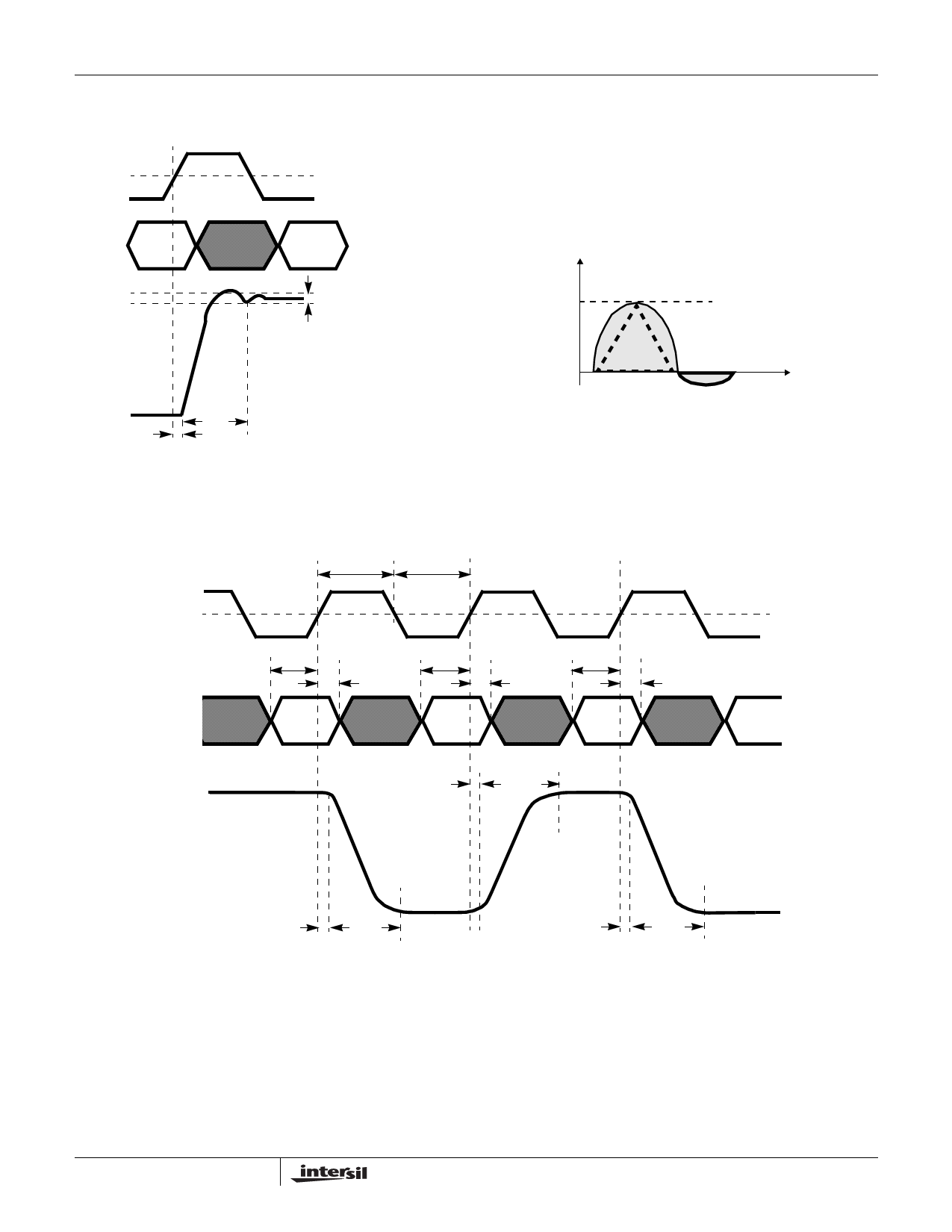

Timing Diagrams

HI5828

CLK

50%

D11-D0

IOUT

1/2 LSB ERROR BAND

tSETT

tPD

FIGURE 2. OUTPUT SETTLING TIME DIAGRAM

V

GLITCH AREA = 1/2 (H x W)

HEIGHT (H)

WIDTH (W)

t (ps)

FIGURE 3. PEAK GLITCH AREA (SINGLET) MEASUREMENT

METHOD

CLK

D11-D0

IOUT

tPW1

tPW2

tSU

tSU

tSU

tHLD

tHLD

tHLD

50%

tPD

tSETT

tPD

tSETT

tPD

tSETT

FIGURE 4. PROPAGATION DELAY, SETUP TIME, HOLD TIME AND MINIMUM PULSE WIDTH DIAGRAM

11