AIC1570CS 查看數據表(PDF) - Analog Intergrations

零件编号

产品描述 (功能)

比赛名单

AIC1570CS

AIC1570CS Datasheet PDF : 18 Pages

| |||

AIC1570

+12V

+3.3VIN

+

Q3

VOUT3

+

COUT3

+

COUT2

Css

+

VCC

VIN2

GATE3

VOUT2

SS

GND

OCSET

UGATE

PHASE

LGATE

PGND

+5VIN

+

Q1

CIN

LOUT

+

VOUT

COUT

Q2

Power Plane Layer

Circuit Plane Layer

Via Connection to Ground Plane

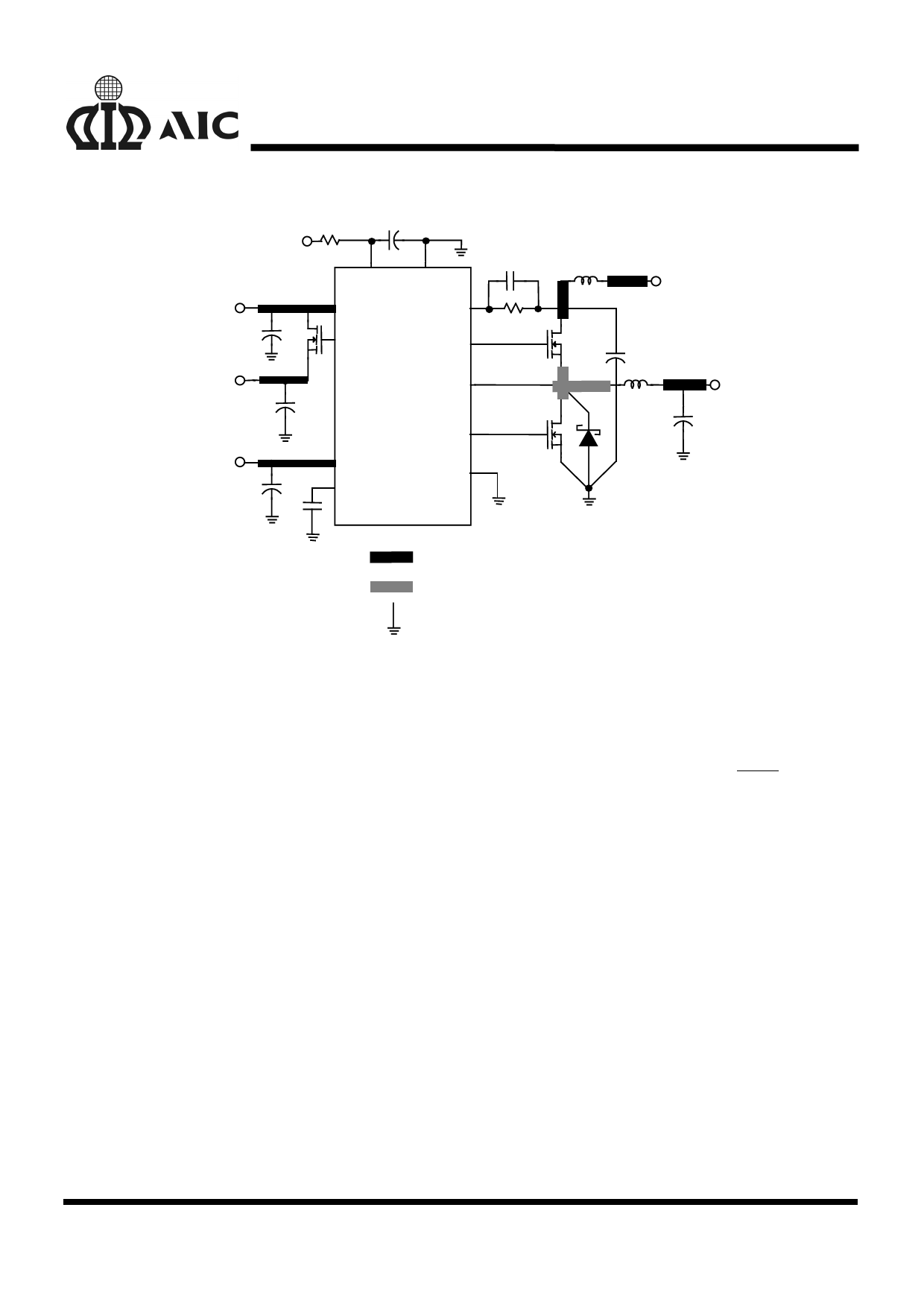

Fig. 11 Printed circuit board power planes and islands

A multi-layer printed circuit board is

recommended. Figure 11 shows the connections

of the critical components in the converter. The

CIN and COUT could each represent numerous

physical capacitors. Dedicate one solid layer for a

ground plane and make all critical component

ground connections with vias to this layer.

PWM Output Capacitors

The load transient for the microprocessor core

requires high quality capacitors to supply the high

slew rate (di/dt) current demand.

The ESR (equivalent series resistance) and ESL

(equivalent series inductance) parameters rather

than actual capacitance determine the buck

capacitor values. For a given transient load

magnitude, the output voltage transient change

due to the output capacitor can be note by the

following equation:

∆VOUT

=

ESR

×

∆IOUT

+

ESL

×

∆IOUT

∆T

,

where

∆IOUT is transient load current step.

After the initial transient, the ESL dependent term

drops off. Because the strong relationship

between output capacitor ESR and output load

transient, the output capacitor is usually chosen

for ESR, not for capacitance value. A capacitor

with suitable ESR will usually have a larger

capacitance value than is needed for energy

storage.

A common way to lower ESR and raise ripple

current capability is to parallel several capacitors.

In most case, multiple electrolytic capacitors of

small case size are better than a single large

14