LP62E16512-T 查看數據表(PDF) - AMIC Technology

零件编号

产品描述 (功能)

比赛名单

LP62E16512-T Datasheet PDF : 14 Pages

| |||

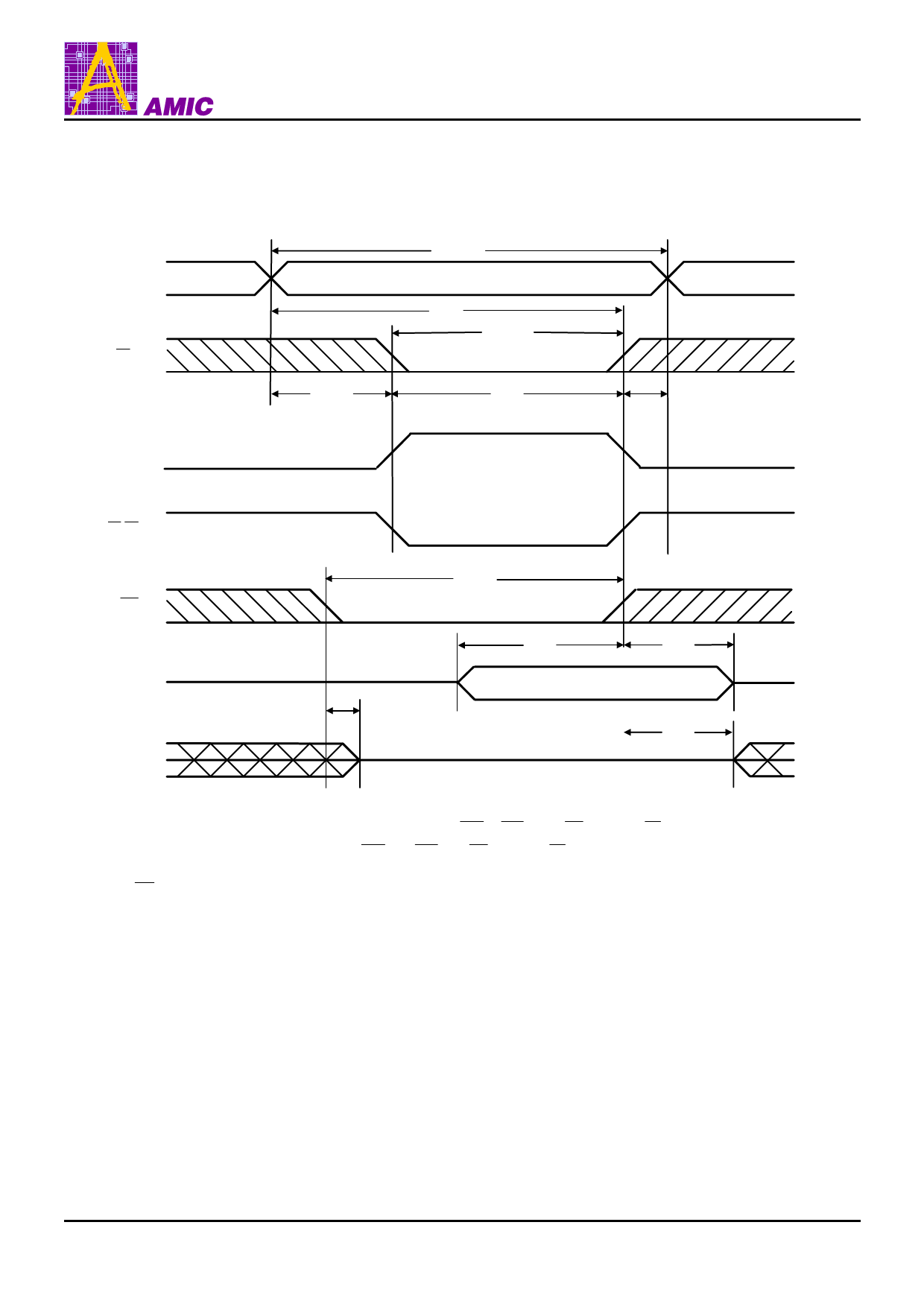

Timing Waveforms (continued)

Write Cycle 3

(Byte Enable Controlled)

Address

CS1

tAS1

CS2

tWC

tAW

tCW1 , tCW2

tBW2

LP62E16512-T Series

tWR3

HB, LB

WE

DATA IN

DATA OUT

tWP

tWHZ4

tDW

tDH

tOW

Notes: 1. tAS is measured from the address valid to the beginning of Write.

2. A Write occurs during the overlap (tWP, tBW) of a low CS1 , WE and ( HB and , or LB ) or a high CS2.

3. tWR is measured from the earliest of CS1 or WE or ( HB and , or LB ) going high or CS2 going Low to the end of the

Write cycle.

4. OE level is high or low.

5. Transition is measured ±200mV from steady state. This parameter is sampled and not 100% tested.

(August, 2004, Version 1.1)

10

AMIC Technology, Corp.