MB90455 查看數據表(PDF) - Fujitsu

零件编号

产品描述 (功能)

比赛名单

MB90455 Datasheet PDF : 78 Pages

| |||

MB90455 Series

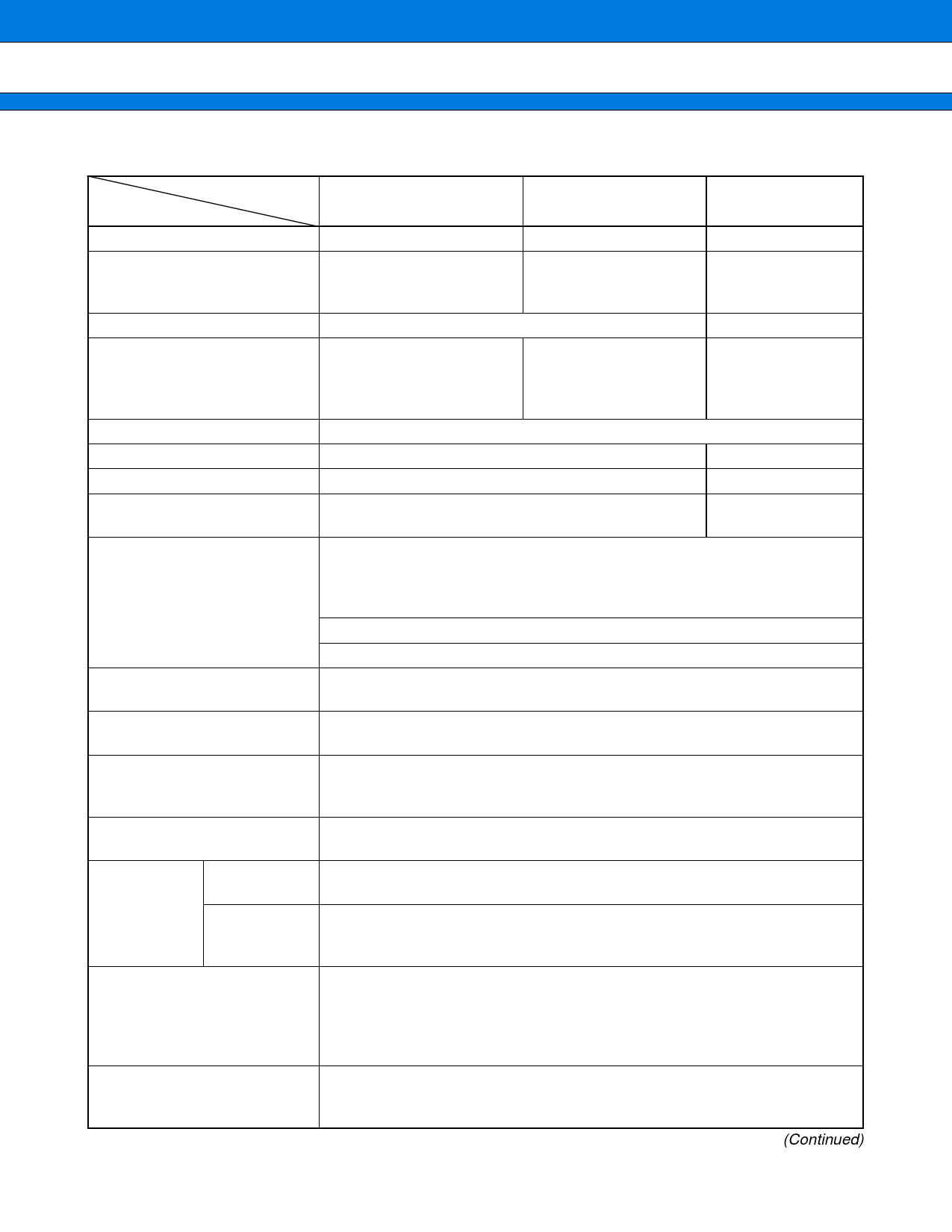

s PRODUCT LINEUP

Parameter

Part Number

MB90F455 (S) /

F456 (S) /F457 (S)

MB90455 (S) /

456 (S) /457 (S)

MB90V495G

Classification

Flash ROM

Mask ROM

Evaluation product

ROM capacity

MB90F455 (S) : 24 Kbytes MB90455 (S) : 24 Kbytes

MB90F456 (S) : 32 Kbytes MB90456 (S) : 32 Kbytes

MB90F457 (S) : 64 Kbytes MB90457 (S) : 64 Kbytes

RAM capacity

2 Kbytes

6 Kbytes

Clock

MB90F455/F456/F457 : MB90455/456/457 :

2 systems

2 systems

MB90F455S/F456S/F457S : MB90455S/456S/457S :

1 system

1 system

2 systems

Process

CMOS

Package

LQFP-48 (0.50 mm width)

PGA256

Operating power supply voltage

3.5 V to 5.5 V

4.5 V to 5.5 V

Special power supply for

emulator*1

None

CPU functions

Number of basic instructions : 351 instructions

Instruction bit length

: 8 bits and 16 bits

Instruction length

: 1 byte to 7 bytes

Data bit length

: 1 bit, 8 bits, 16 bits

Minimum instruction execution time : 62.5 ns (at 16-MHz machine clock)

Interrupt processing time : 1.5 µs at minimum (at 16-MHz machine clock)

Low power consumption

(standby) mode

Sleep mode/Clock mode/Time-base timer mode/

Stop mode/CPU intermittent

I/O port

General-purpose input/output ports (CMOS output) : 34 ports (36 ports*2)

including 4 high-current output ports (P14 to P17)

Time-base timer

18-bit free-run counter

Interrupt cycle : 1.024 ms, 4.096 ms, 16.834 ms, 131.072 ms

(with oscillation clock frequency at 4 MHz)

Watchdog timer

Reset generation cycle: 3.58 ms, 14.33 ms, 57.23 ms, 458.75 ms

(with oscillation clock frequency at 4 MHz)

16-bit input/

output timer

16-bit free-run

timer

Input capture

Number of channels: 1

Interrupt upon occurrence of overflow

Number of channels: 4

Retaining free-run timer value set by pin input (rising edge, falling edge, and

both edges)

16-bit reload timer

Number of channels: 2

16-bit reload timer operation

Count clock cycle: 0.25 µs, 0.5 µs, 2.0 µs

(at 16-MHz machine clock frequency)

External event count is allowed.

Clock timer

15-bit free-run counter

Interrupt cycle: 31.25 ms, 62.5 ms, 12 ms, 250 ms, 500 ms, 1.0 s, 2.0 s

(with 8.192 kHz sub clock)

(Continued)

4