P80C557E4 查看數據表(PDF) - Philips Electronics

零件编号

产品描述 (功能)

比赛名单

P80C557E4 Datasheet PDF : 72 Pages

| |||

Philips Semiconductors

Single-chip 8-bit microcontroller

Product specification

P83C557E4/P80C557E4/P89C557E4

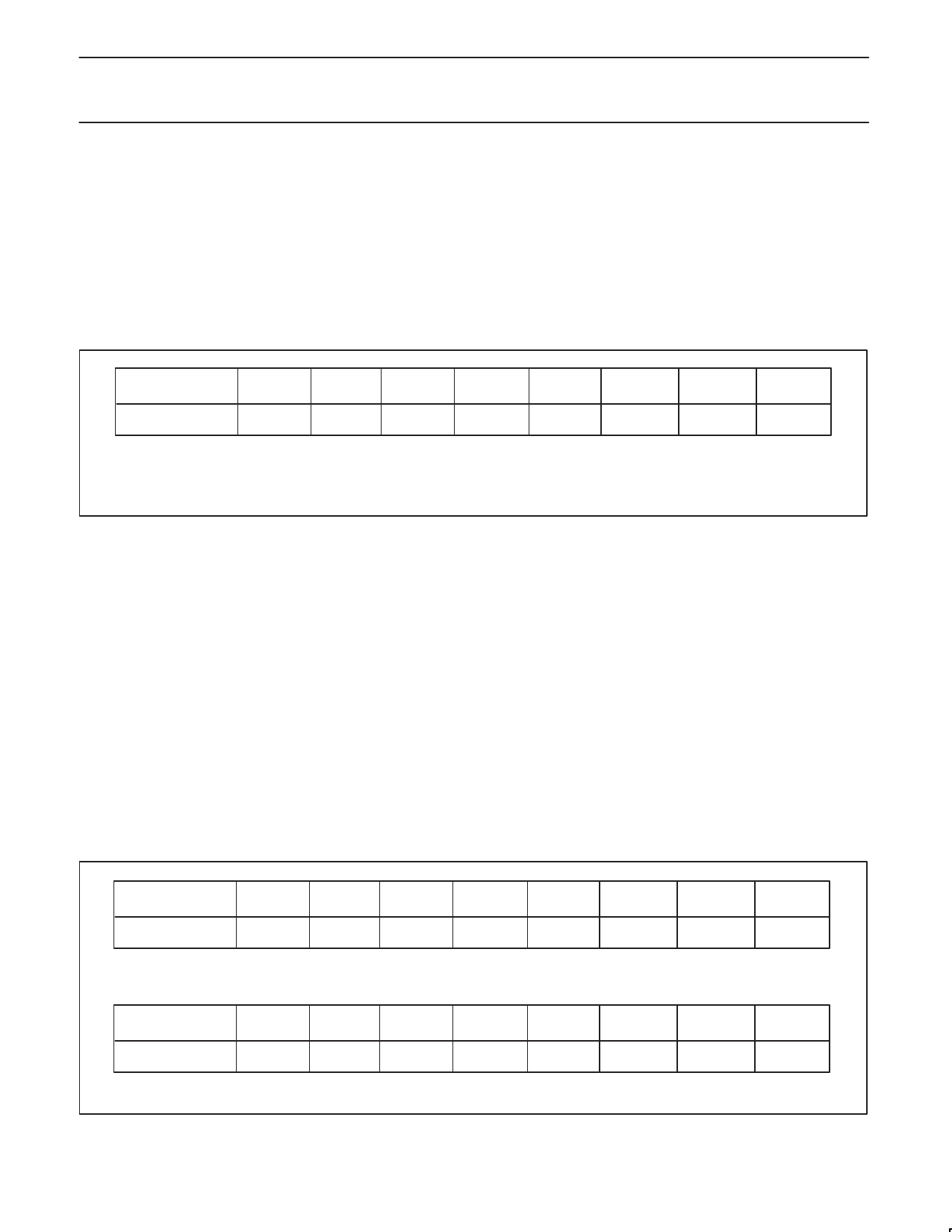

A/D Input Port Scan-Select Register ADPSS

The Special Function Register ADPSS contains control bits to select

the analog input channel(s) to be scanned for A/D conversion. The

reset value of ADPSS is (00000000). Its hardware address is E7H.

ADPSS is not bit addressable.

If all bits are ‘0’ then no A/D conversion can be started. If ADPSS is

written while an A/D conversion is in progress (ADSST in the

ADCON register is ‘1’) then the autoscan loop with the previous

selected analog inputs is completed first. The next autoscan loop is

performed with the new selected analog inputs.

7

6

5

4

3

2

1

0

ADPSS (E7H)

ADPSS7 ADPSS6 ADPSS5 ADPSS4 ADPSS3 ADPSS2 ADPSS1 ADPSS0

ADPSS7–0 For each individual bit position:

0 = The corresponding analog input is skipped in the auto-scan loop.

1 = The corresponding analog input is included in the auto-scan loop.

Figure 16. A/D input port scan-select register.

A/D Result Registers ADRSLn and ADRSH:

The binary result code of A/D conversions is accessed by these

Special Function Registers. The result SFR are read only registers.

The read value after reset is indeterminate. Their data are not

affected by chip reset. They are not bit addressable.

There are 8 Special Function Registers ADRSLn

(ADRSL0...ADRSL7) – A/D Result Low byte – and one general SFR

ADRSH – A/D Result High byte – . Each of ADRSLn is associated

with the coincidently indexed analog input channel ADCn

(ADC0/P5.0...ADC7/P5.7). Reading an ADRSLn register by

software copies at the same time the two highest bits of the 10-bit

conversion result into two latches, thus preserving them until the

next read of any ADRSLn register. These two latches form bit

positions 0 and 1 of SFR ADRSH, the upper 6 bits of ADRSH are

always read as ’0’.

Thus it is ensured to get the 10-bit result of the same single A/D

conversion by reading any register ADRSLn first and after it the

register ADRSH.

ADRSLn

(n: 0...7)

ADRSH

7

6

5

4

3

2

ADRSn.7 ADRSn.6 ADRSn.5 ADRSn.4 ADRSn.3 ADRSn.2

1

0

ADRSn.1 ADRSn.0

7

6

5

4

3

0

0

0

0

0

Figure 17. A/D Result Registers.

2

1

0

0

ADRSn.9 ADRSn.8

1999 Mar 02

19