PD1394P11ABD 查看數據表(PDF) - Philips Electronics

零件编号

产品描述 (功能)

比赛名单

PD1394P11ABD Datasheet PDF : 20 Pages

| |||

Philips Semiconductors

3-port physical layer interface

Preliminary specification

PDI1394P11A

associated link controller. The received data is also transmitted out

the other active cable ports.

The cable status, bus initialization and arbitration states are

monitored through the cable interface using differential comparators.

The outputs of these comparators are used by internal logic to

determine cable and arbitration status. The TPA channel monitors

the incoming cable common-mode voltage value during arbitration to

determine the speed of the next packet transmission. The TPB

channel monitors the incoming cable common-mode voltage for the

presence of the remotely supplied twisted-pair bias voltage,

indicating the cable connection status.

The PDI1394P11A provides a nominal 1.85 V for driver load

termination. This bias voltage, when seen through a cable by a

remote receiver, is used to sense the presence of an active

connection. The value of this bias voltage has been chosen to allow

inter-operability between transceiver chips operating from either 5 V

nominal supplies, or 3.3 V nominal supplies. This bias voltage

source should be stabilized by using an external filter capacitor. When

not powered, the PDI1394P11A prevents the bias voltage from

erroneously powering up the part as is seen in some other Phys.

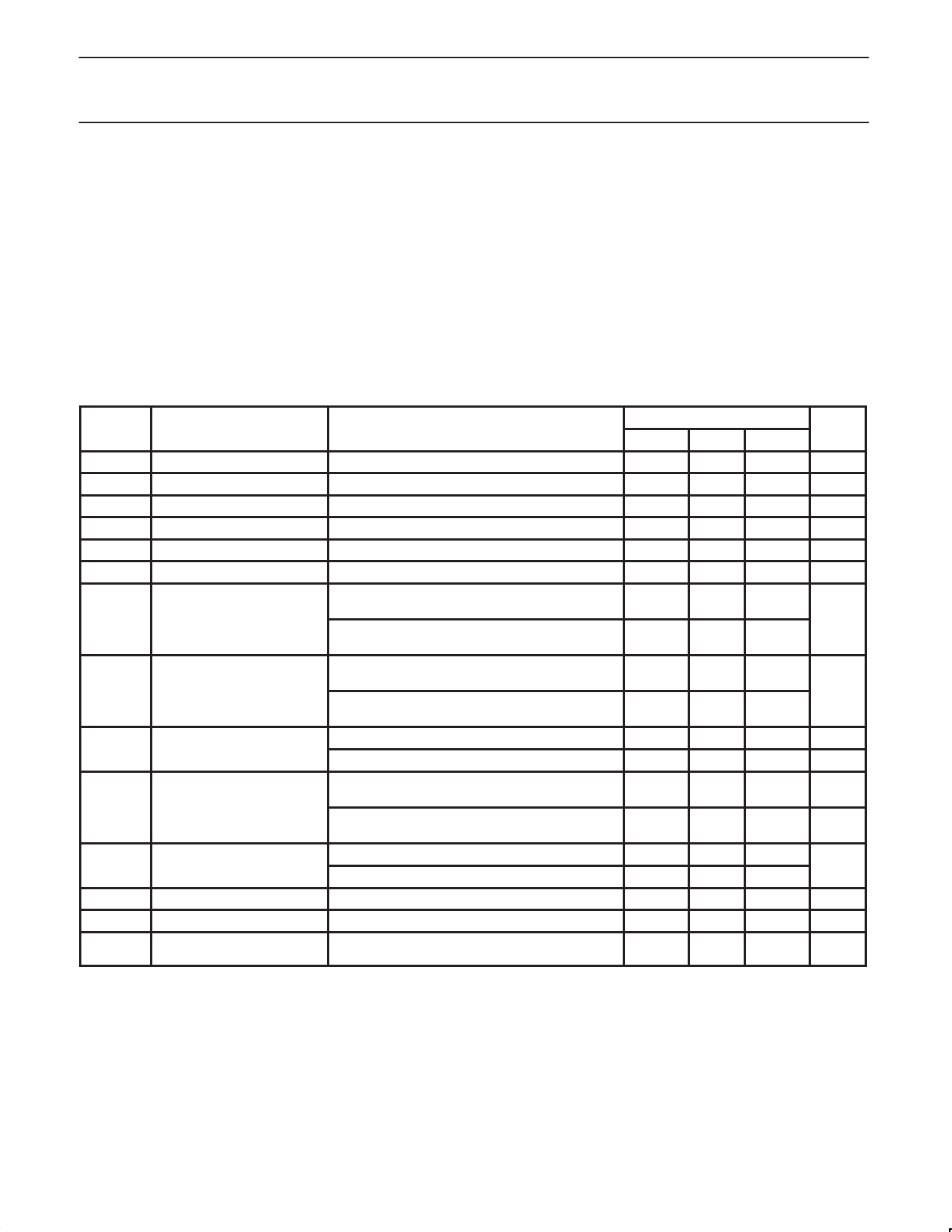

8.0 RECOMMENDED OPERATING CONDITIONS

SYMBOL

PARAMETER

CONDITION

VDD

VIH

VIL

VID–100

VID–200

VID–ARB

DC supply voltage

High level input voltage

Low level input voltage

Differential input voltage

Differential input voltage

Differential input voltage

VIC–100 Common mode voltage

VIC–200SP Common mode voltage

Receive input jitter

Receive input skew

IOL/IOH Output current, IOL/IOH

IO

fXTAL

Tamb

Output current

Crystal frequency

Operating ambient

temperature range in free air

Source/non-source power node

CMOS inputs

CMOS inputs

Cable inputs, 100Mbit operation

Cable inputs, 200Mbit operation

Cable inputs, during arbitration

TPB cable inputs, 100Mbit or speed signaling OFF,

source power node

TPB cable inputs, 100Mbit or speed signaling OFF,

non–source power node

TPB cable inputs, 200Mbit or speed signaling,

source power node

TPB cable inputs, 200Mbit or speed signaling,

non–source power node

TPA, TPB cable inputs, 100Mbit operation

TPA, TPB cable inputs, 200Mbit operation

Between TPA and TPB cable inputs, 100Mbit

operation

Between TPA and TPB cable inputs, 200Mbit

operation

SYSCLK

Control, Data, CNA, C/LKON

TPBIAS outputs

Parallel resonant fundamental mode crystal

MIN

2.7

2.0

142

132

171

1.165

LIMITS

TYP

3.3

MAX

3.6

5.5

0.8

260

260

262

2.515

1.165

2.015

0.935

2.515

0.935

2.015

±1.08

±0.5

±0.8

±0.55

–16

–12

–3

24.5735

24.576

16

12

1.3

24.5785

0

+70

UNIT

V

V

V

mV

mV

mV

V

V

ns

ns

ns

ns

mA

mA

MHz

°C

1999 Mar 10

5