PMB2100 查看數據表(PDF) - Infineon Technologies

零件编号

产品描述 (功能)

比赛名单

PMB2100 Datasheet PDF : 20 Pages

| |||

3

Application

3.1

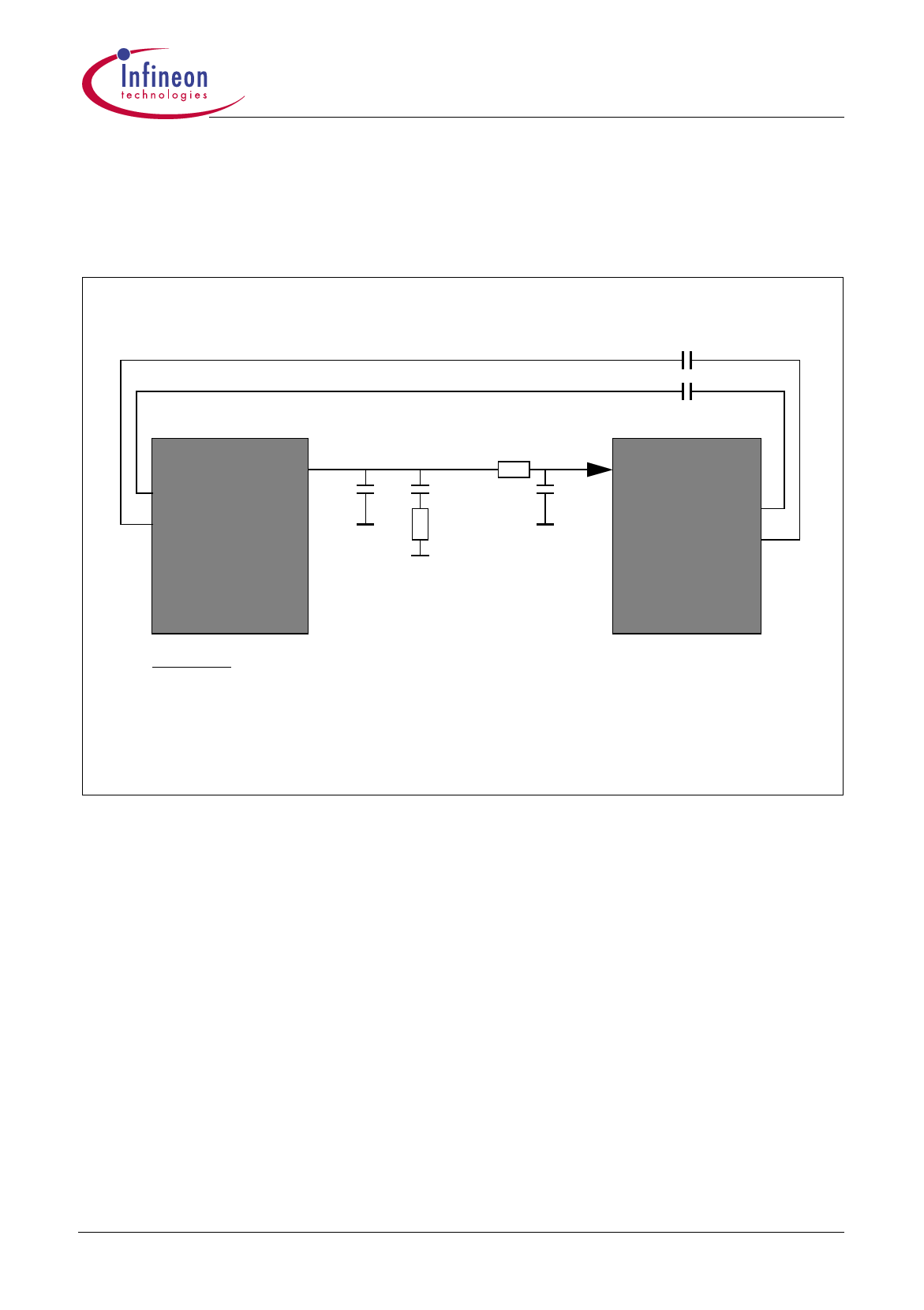

Application Circuit

PMB 2100

Version 1.1

Application

12p

CPLO1

LO1

560p

LO1X

PMB6250

PMB6253

3k3

5.6n

3k3

12p

270p

VTUNE

OUT

OUTX

VCO

PMB2100

SMARTi.

Icp, fractional: 1.2 mA 20%

Icp, integer: 2.0 mA 20%

The SAM timer is set to 115us.

Figure 3-1 Application Circuit

Locking times of less than 200us for 10° peak phase error,

more than -50dB of loop suppression at 400kHz offset,

a RMS phase error less than 1.5° without other impacts

are typical values reached with this design.

Appl_circuit.wmf

3.2

Hints

DC blocking capacitors must be used between RF outputs and SMARTi LO1 inputs.

Specification

12

2001-07-30