CD3206BB 查看數據表(PDF) - Philips Electronics

零件编号

产品描述 (功能)

比赛名单

CD3206BB Datasheet PDF : 18 Pages

| |||

Philips Semiconductors

9-bit latched/registered/pass-thru Futurebus+ transceiver

Product specification

FB2031

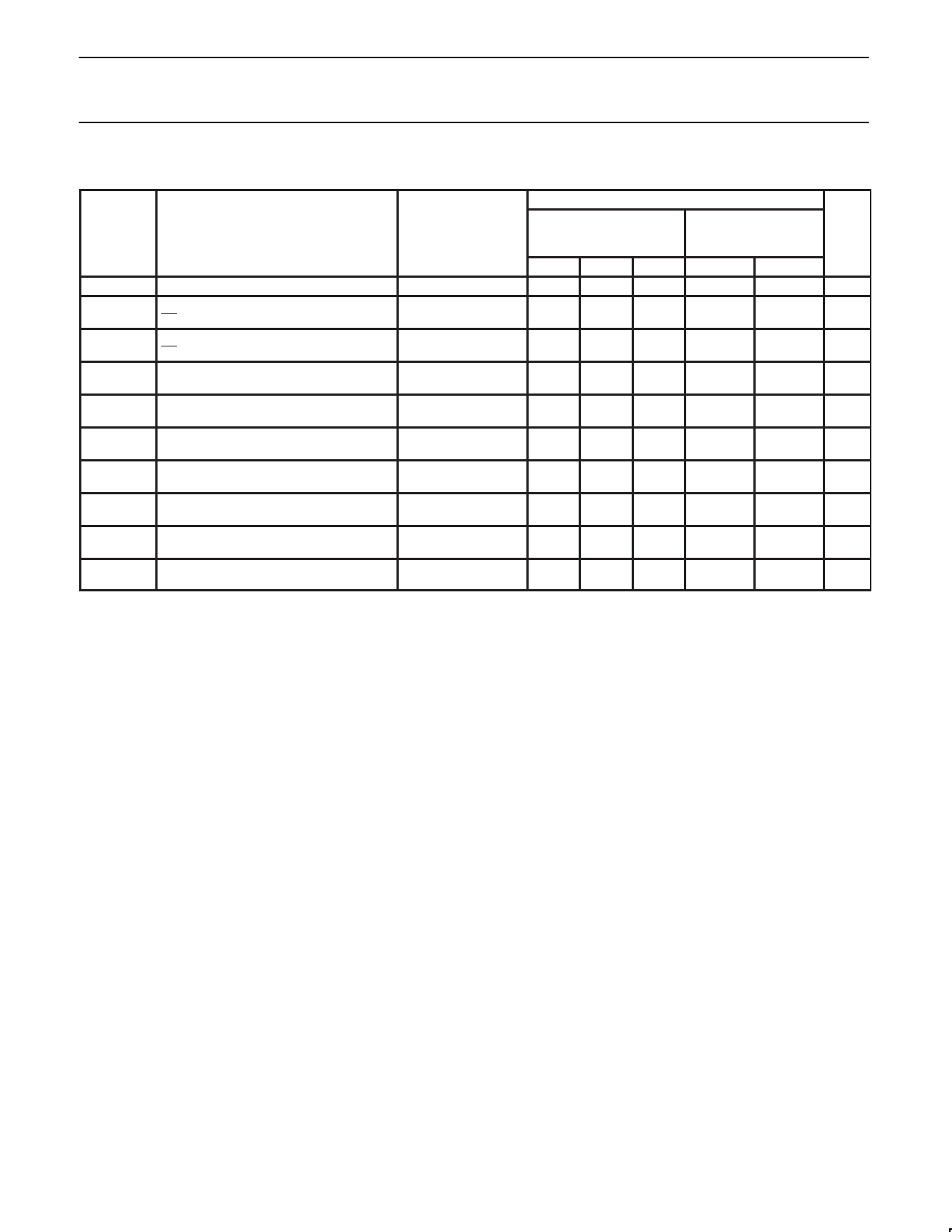

AC ELECTRICAL CHARACTERISTICS (Commercial)

A PORT LIMITS

SYMBOL

PARAMETER

TEST

CONDITION

Tamb = +25°C, VCC = 5V,

CL = 50pF, RL = 500Ω

MIN TYP MAX

Tamb = 0 to +70°C,

VCC = 5V±10%,

CL = 50pF, RL = 500Ω

MIN

MAX

UNIT

fMAX

tPLH

tPHL

tPLH

tPHL

tPLH

tPHL

tPLH

tPHL

tPZH

tPZL

tPHZ

tPLZ

tTLH

tTHL

tSK(o)

tSK(p)

Maximum clock frequency

Propagation delay (thru mode)

Bn to An

Propagation delay (transparent latch)

Bn to An

Propagation delay

LCBA to An

Propagation delay

SEL0 or SEL1 to An

Output enable time from High or Low

OEA to An

Output disable time to High or Low

OEA to An

Output transition time, An Port

10% to 90%, 90% to 10%

Output to output skew for multiple

channels1

Pulse skew 2

tPHL – tPLH MAX

Waveform 4

120 150

100

Waveform 1, 2

2.5

4.4

5.9

2.4

4.2

5.5

2.3

2.4

Waveform 1, 2

2.9

4.6

6.2

2.8

4.3

5.9

2.7

2.5

Waveform 1, 2

2.6

4.1

5.5

2.4

4.7

6.1

2.0

2.0

Waveform 1, 2

1.5

3.8

5.2

1.7

3.9

6.0

1.2

1.5

Waveform 5, 6

2.1

3.5

4.8

2.0

3.8

5.3

1.8

1.7

Waveform 5, 6

1.9

3.4

4.8

1.7

3.2

4.8

1.6

1.5

Test Circuit and

2.0

Waveforms

1.0

Waveform 3

0.5

1.0

Waveform 2

0.5

1.0

MHz

6.6

5.9

ns

7.0

6.5

ns

6.0

6.5

ns

6.0

6.5

ns

5.8

6.0

ns

5.4

5.4

ns

7.5

3.5

ns

1.5

ns

1.0

ns

NOTES:

1. tPNactual – tPMactual for any data input to output path compared to any other data input to output path where N and M are either LH or HL.

Skew times are valid only under same test conditions (temperature, VCC, loading, etc.).

2. tSK(p) is used to quantify duty cycle characteristics. In essence it compares the input signal duty cycle to the corresponding output signal

duty cycle (50MHz input frequency and 50% duty cycle, tested on data paths only).

1995 May 25

11