82C88 查看數據表(PDF) - Intersil

零件编号

产品描述 (功能)

比赛名单

82C88 Datasheet PDF : 11 Pages

| |||

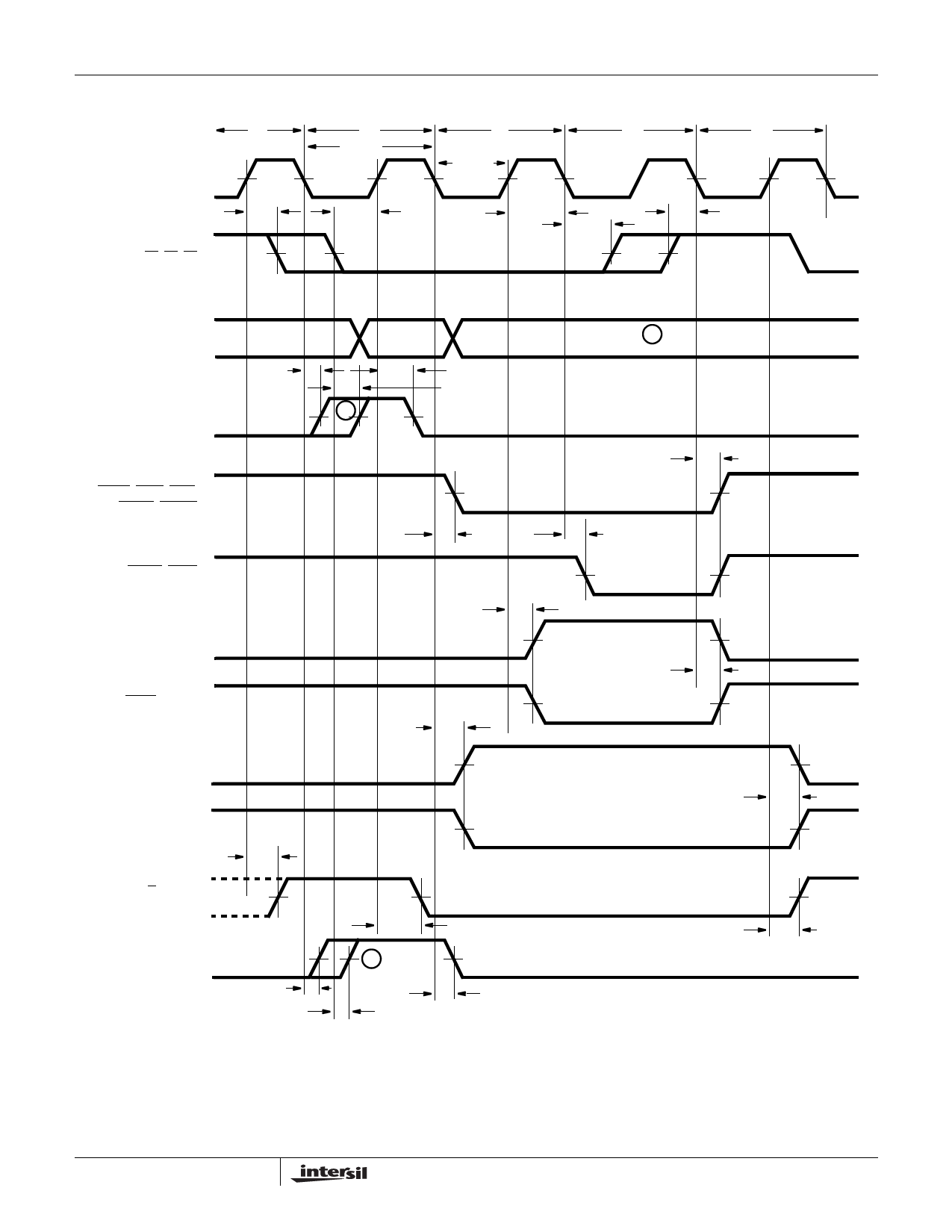

Timing Waveforms (Note 3)

STATE

T4

CLK

TCHSV

(5)

T1

TCLCL

(1)

TSVCH

(4)

S2, S1, S0

82C88

T2

TCLCH

(2)

TCHCL

(3)

T3

TCLSH

(7)

T4

TSHCL

(6)

ADDRESS/DATA

ALE

TCLLH

(10)

ADDRESS

VALID

TCHLL (14)

TSVLH (12)

2

WRITE 1

DATA VALID

MRDC, IORC, INTA,

AMWC, AIOWC

TCLML

(15)

TCLML

(15)

TCLMH

(16)

MWTC, IOWC

DEN (READ)

(INTA)

PDEN (READ)

(INTA)

DEN (WRITE)

TCVNV

(8)

TCVNV

(8)

TCVNX

(9)

PDEN (WRITE)

TCHDTH

(18)

TCVNX

(9)

DT/R (READ)

(INTA)

MCE

TCHDTL

(17)

2

TCHDTH

(18)

NOTES:

TCLMCH

(11)

TSVMCH

(13)

TCVNX

(9)

1. Address/Data Bus is shown only for reference purposes.

2. Leading edge of ALE and MCE is determined by the falling edge of CLK or status going active. Whichever occurs last.

3. All timing measurements are made at 1.5V unless otherwise specified.

FIGURE 1.

8

FN2979.2

August 25, 2005