MB90440G 查看數據表(PDF) - Fujitsu

零件编号

产品描述 (功能)

比赛名单

MB90440G Datasheet PDF : 61 Pages

| |||

MB90440G Series

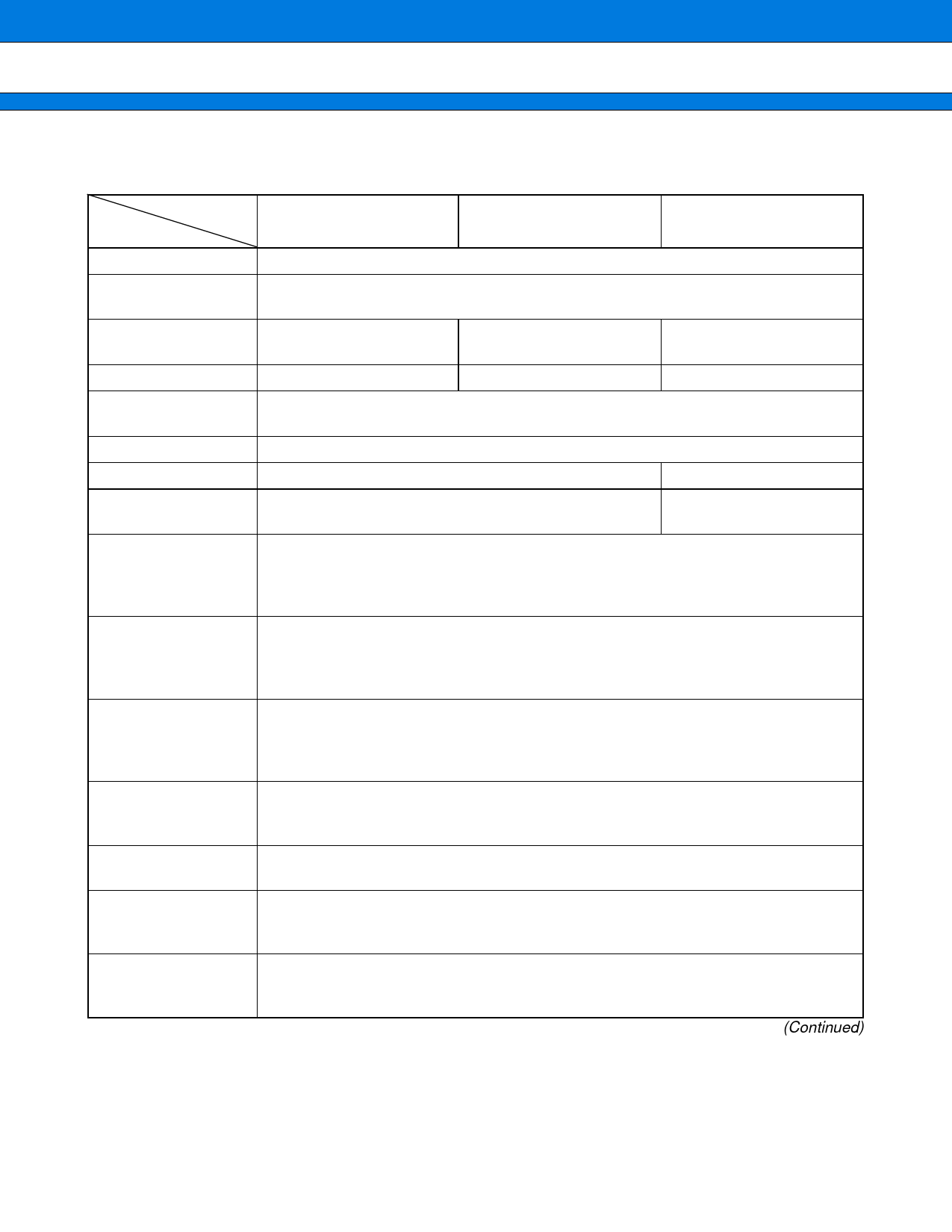

s PRODUCT LINEUP

The following table provides a quick outlook of the MB90440G Series

Part number

Parameter

MB90443G

(under development)

MB90F443G

MB90V440G

CPU

F2MC-16LX CPU

System clock

On-chip PLL clock multiplier (×1, ×2, ×3, ×4, 1/2 when PLL stops)

Minimum instruction execution time : 62.5 ns (4 MHz osc. PLL ×4)

ROM size

Mask ROM

128 Kbytes

Flash memory

128 Kbytes

External

RAM size

6 Kbytes

6 Kbytes

14 Kbytes

Operating*1

voltage range

5 V ± 10%

Temperature range

−40 °C to +105 °C

Package

QFP100

PGA-256

Voltage dedicated for

emulator*2

No

UART0

Full duplex double buffer

Supports clock asynchronous/synchronous (with start/stop bits) transfer

Baud rate : 4808/5208/9615/10417/19230/38460/62500/500000 bps (asynchronous)

500 K/1 M/2 Mbps (synchronous) at System clock = 16 MHz

UART1

(SCI)

Full duplex double buffer

Asynchronized (start/stop bits synchronized) and CLK-synchronous communication

Baud rate : 601 bps to 250 kbps (asynchronous)

31.25 kbps to 2 Mbps (synchronous)

Serial IO

Transfer can be started from MSB or LSB

Supports internal clock synchronized transfer and external clock synchronized transfer

Supports positive-edge and negative-edge clock synchronization

Baud rate : 31.25 K/62.5 K/125 K/500 K/1 M/2 Mbps at System clock = 16 MHz

8/10 bit

A/D Converter

10-bit or 8-bit resolution

8 input channels

Conversion time : 6.12 µs (per one channel)

16-bit Reload Timer

(2 channels)

Operation clock frequency : fsys/21, fsys/23, fsys/25 (fsys = System clock frequency)

Supports External Event Count function

16-bit

I/O Timer

Signals an interrupt during overflow

Supports Timer Clear during a match with Output Compare (Channel 0)

Operation clock freq. : fsys/22, fsys/24, fsys/26, fsys/28 (fsys = System clock freq.)

16-bit

Output Compare

(4 channels)

Signals an interrupt during a match with 16-bit I/O Timer

Four 16-bit compare registers

A pair of compare registers can be used to generate an output signal

(Continued)

4