HM-65262/883 查看數據表(PDF) - Intersil

零件编号

产品描述 (功能)

比赛名单

HM-65262/883 Datasheet PDF : 10 Pages

| |||

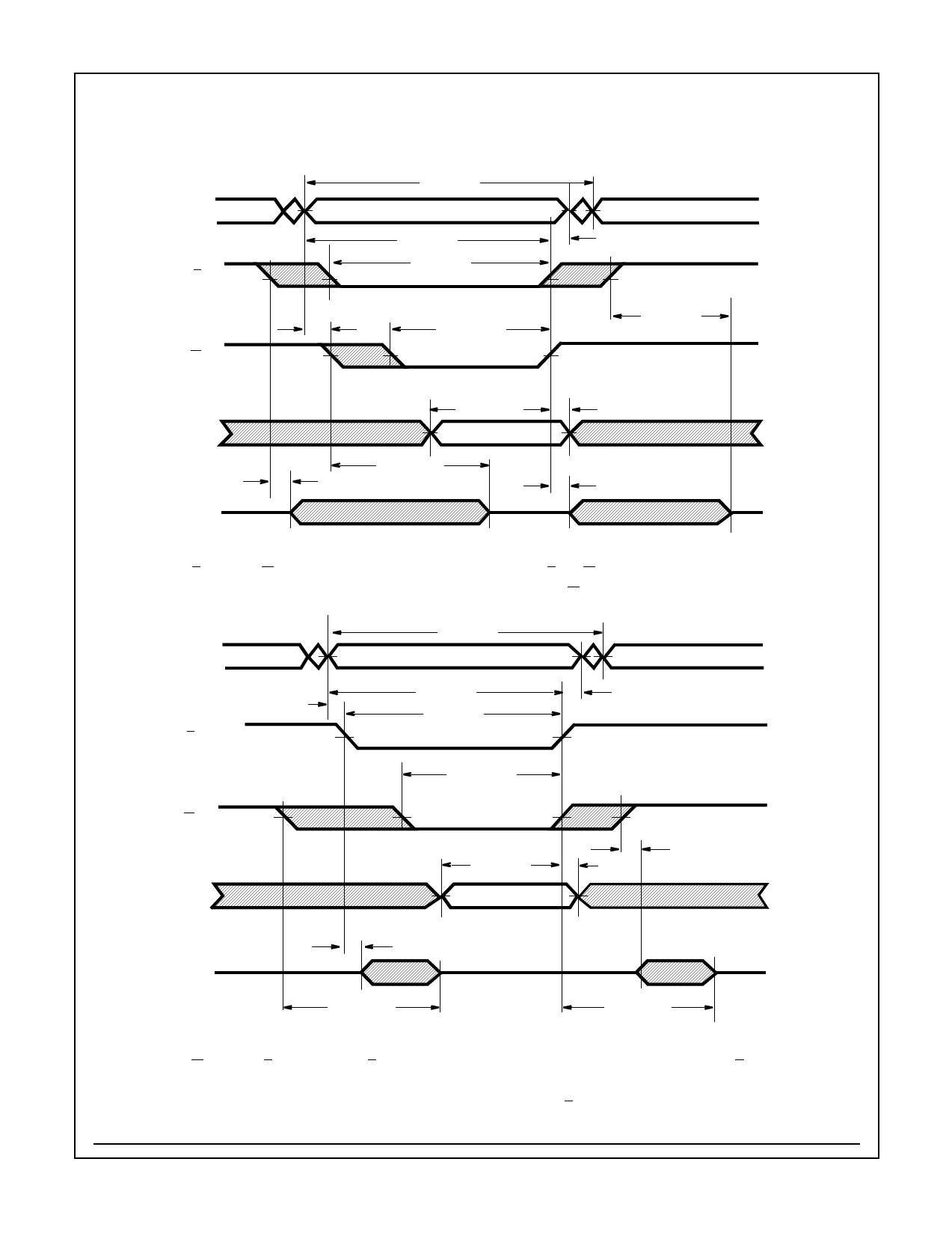

Timing Waveforms (Continued)

HM-65262/883

(1) TAVAX

A

(7) TAVWH

(5) TWHAX

(3) TELWH

E

(6)

TAVWL

(11) TWLWH

(21) TEHQZ

W

(12) TDVWH

(13) TWHDX

D

(20)

TELQX

(18) TWLQZ

Q

(19) TWHQX

NOTE:

1. In this mode, E rises after W. The address must remain stable whenever both E and W are low.

FIGURE 3. WRITE CYCLE 1: CONTROLLED BY W (LATE WRITE)

(1) TAVAX

A

(8) TAVEL

E

(10) TAVEH

(14) TELEH

(9) TEHAX

(15) TWLEH

W

(16) TDVEH

(17)

TEHDX

(19) TWHQX

D

(20) TELQX

Q

(18) TWLQZ

(21) TEHQZ

NOTE:

1. In this mode, W rises after E. If W falls before E by a time exceeding TWLQZ (Max) TELQX (Min), and rises after E by a time exceeding

TEHQZ (Max) TWHQZ (Min), then Q will remain in the high impedance state throughout the cycle.

FIGURE 4. WRITE CYCLE 2: CONTROLLED BY E (EARLY WRITE)

Low Voltage Data Retention

210