EDI88128C 查看數據表(PDF) - Unspecified

零件编号

产品描述 (功能)

比赛名单

EDI88128C Datasheet PDF : 8 Pages

| |||

EDI88128C

AC C R C HARACTERISTICS

EAD

YCLE

(VCC = 5.0V, VSS = 0V, TA = -55°C TO +125°C)

Symbol

Parameter

JEDEC

Alt.

Read Cycle Time

tAVAV

tRC

Address Access Time

tAVQV

tAA

Chip Select Access Time

tELQV

tACS

tSHQV

tACS

Chip Select to Output in Low Z (1)

tELQX

tCLZ

tSHQX

tCLZ

Chip Disable to Output in High Z (1)

tEHQZ

tCHZ

tSLQZ

tCHZ

Output Hold from Address Change

tAVQX

tOH

Output Enable to Output Valid

tGLQV

tOE

Output Enable to Output in Low Z (1)

tGLQX

tOLZ

Output Disable to Output in High Z (1)

tGHQZ

tOHZ

1. This parameter is guaranteed by design but not tested.

70ns

Min

70

Max

70

70

70

3

3

0

30

0

30

3

25

0

0

30

85ns

Min

85

Max

85

85

85

3

3

0

30

0

30

3

30

0

0

30

100ns

Min

Max

100

100

100

100

3

3

0

30

0

30

3

50

0

0

30

Units

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

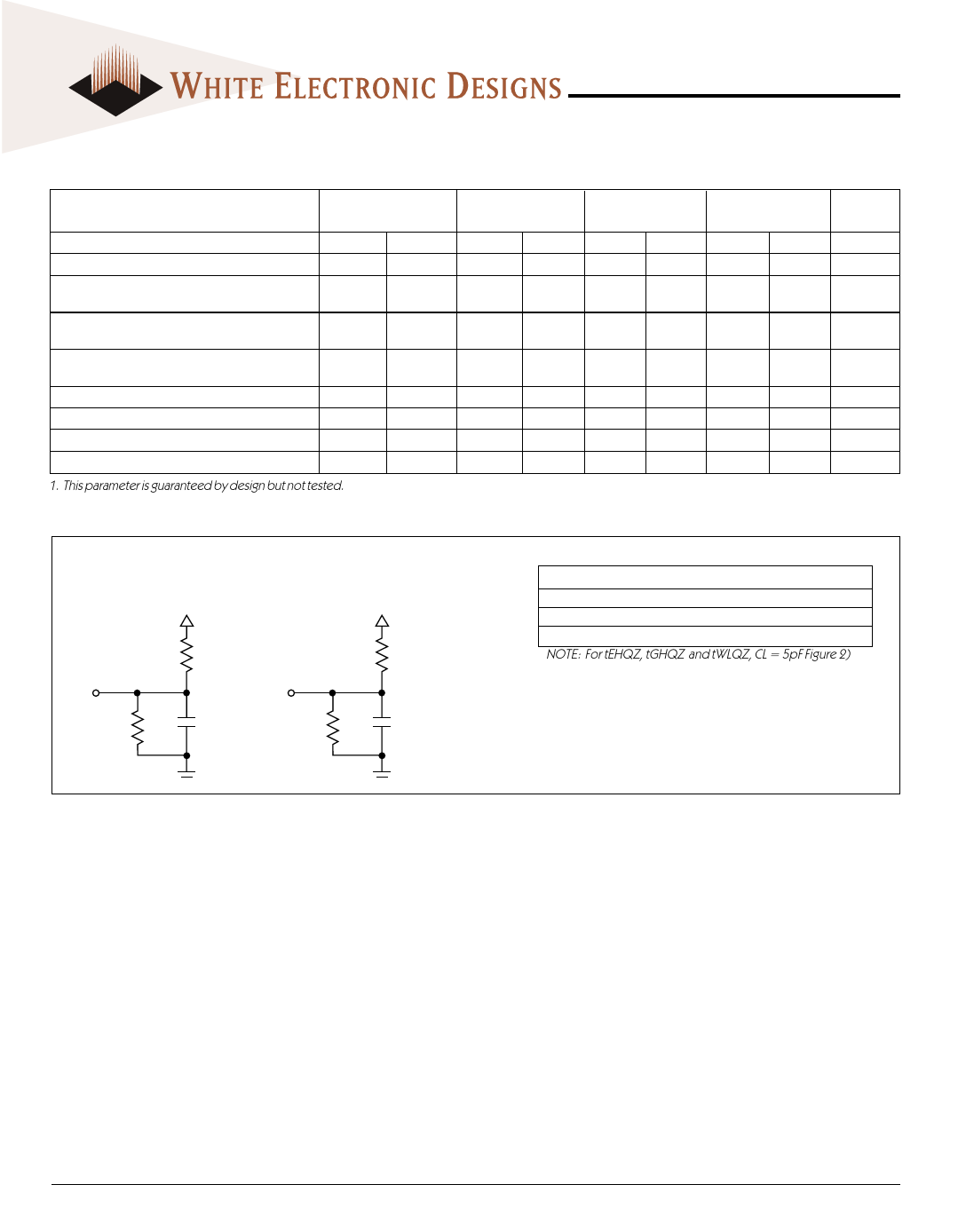

AC T C EST

ONDITIONS

Figure 1

Vcc

Figure 2

Q

255Ω

480Ω

30pF

Q

255Ω

Vcc

480Ω

5pF

Input Pulse Levels

VSS to 3.0V

Input Rise and Fall Times

5ns

Input and Output Timing Levels

1.5V

Output Load

Figure 1

NOTE: For tEHQZ, tGHQZ and tWLQZ, CL = 5pF Figure 2)

3

White Electronic Designs Corporation • (602) 437-1520 • www.whiteedc.com