MS622424 查看數據表(PDF) - Mosel Vitelic, Corp

零件编号

产品描述 (功能)

比赛名单

MS622424 Datasheet PDF : 11 Pages

| |||

MOSEL VITELIC

MS622424

Pin Descriptions (Cont’d)

Pin Name

RSB

AFB

FFB

VSS/TEST

BD.REV(0-3)

Description

Reset input pin. This asynchronous system reset initializes state machines and

resets the Address, Status, and Color Buffer registers. It also resets the Write

FIFO so that it is empty of any contents. It resets command register bits CB2–CB7

and sets bits CB0–CB1. During a reset, CONFIGBUS0–CONFIGBUS7 are in

tri-state. This pin is active low.

The FIFO status output pin. This active low output indicates that the Write FIFO is

half or almost full. This active low output can be programmed by a bit in the

Command Register to indicate that the FIFO is at least half full or is almost full

(eight or less empty locations left).

The FIFO status output pin. This active low output indicates that the Write FIFO

is full.

This pin should be grounded for normal operation.

Board revision input pins. These input pins can be pull-up to VDD or pull-down to

VSS. The BD.REV data can be read though the revision register.

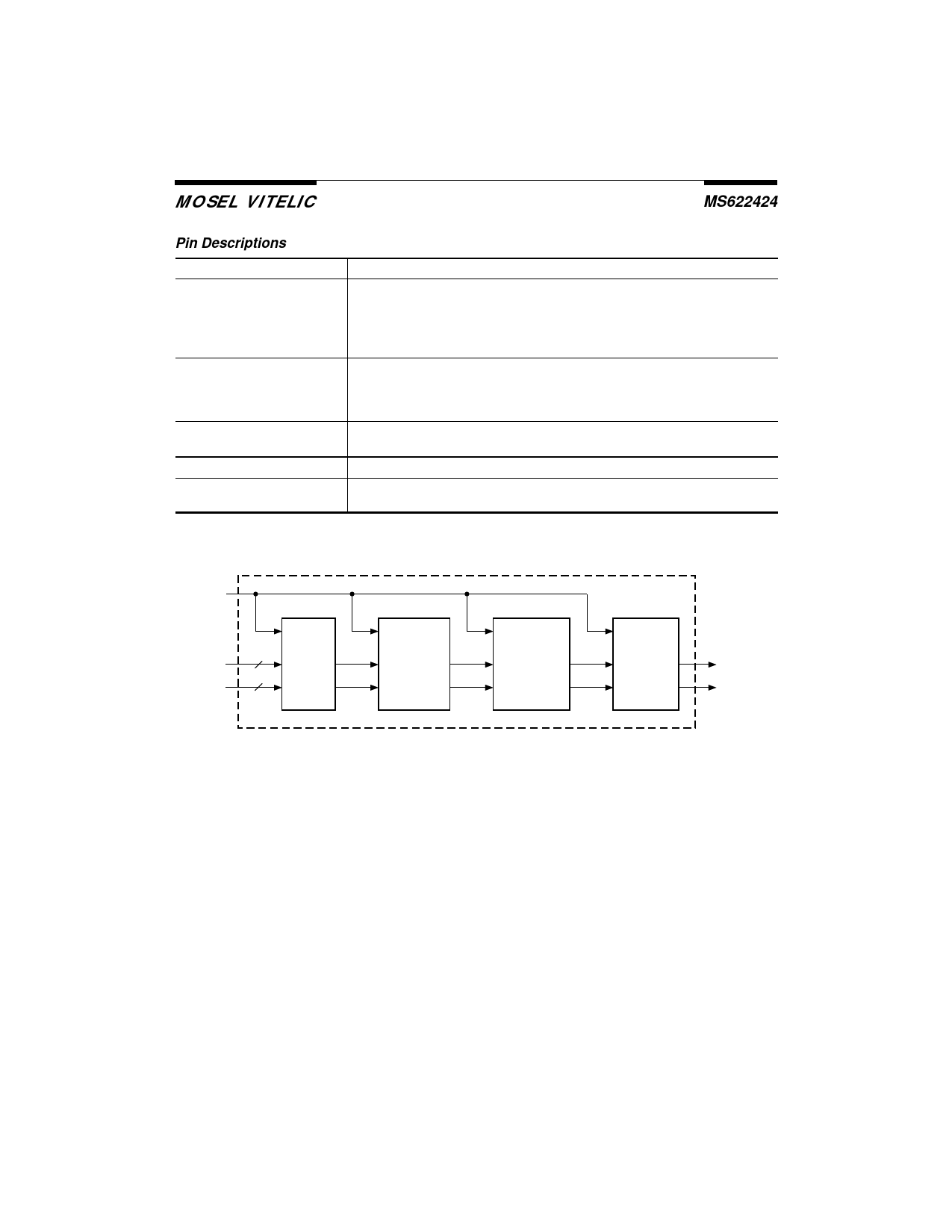

CLOCK.IN

INPUT

24

PIX.IN(0-23)

PIPE.IN(0-3)

4

LATCH 1

ADDRESS

DECODER

LATCH 2

SENSE

AMPLIFIER

LATCH 3

OUTPUT

LATCH 4

POUT(0-23)

PIPE.OUT(0-3)

Internal Pipeline Data Path for Pixel and Pipe Input Data

MS622424 Rev. 1.0 January 1995

8-7