70P2352-IGT 查看數據表(PDF) - Teridian Semiconductor Corporation

零件编号

产品描述 (功能)

比赛名单

70P2352-IGT Datasheet PDF : 42 Pages

| |||

Transmit Driver

In CMI (electrical) mode, the CMIxP/N pins are

biased and terminated off-chip. They interface to

75Ω coaxial cable through a 1:1 wideband

transformer and coaxial RF connectors. Reference

application notes for schematic and layout

guidelines.

The transmitter encodes the data using CMI line

coding and shapes an analog signal to meet the

appropriate ITU-T G.703 template. The CMI outputs

are tri-stated during transmit disable and transmit

power-down for redundancy applications and power-

savings.

Note: To avoid reflections causing unwanted

board noise, it’s recommended to power-down

unused transmit ports that are not terminated

with cable to an Rx input port.

When the CMI pin is low, the chip is in Fiber

(NRZ pass-through) mode and interfaces directly to

an optical transceiver module. The ECLxP/N pins

are internally biased and output NRZ data at

LVPECL levels. The CMI driver, encoder and

decoder are disabled in Fiber (NRZ) mode.

Clock Synthesizer

The transmit clock synthesizer is a low-jitter DLL that

generates a 278.528/311.04 MHz clock for the CMI

encoder. It is also used in both the receive and

transmit sides for clock and data recovery.

This 2x line rate clock is also available at the

TXCKxP/N pins for downstream synchronization or

system debug.

Transmit Backplane Equalizer

An optional fixed LVPECL equalizer is integrated in

the transmit path for architectures that use LIUs on

active interface cards. The fixed equalizer can

compensate for up to 1.5m of FR4 trace and can be

enabled by the TXOUT1 pin or TXEQ bit as follows:

TXOUT1 pin

Low

Float

TXEQ bit

1

0

Tx Equalizer

Enabled

Disabled

Transmit Loss of Lock

In transmit modes using the integrated CDR, the

78P2352 will declare a loss of lock condition when

there is no valid signal detected at the SIxDP/N data

inputs.

Note: The Tx LOL indicator is invalid and

undefined when the parallel (nibble) interface is

selected.

78P2352

Dual Channel

OC-3/ STM1-E/ E4 LIU

POWER-DOWN FUNCTION

Power-down controls are provided to allow the

78P2352 to be shut off. Transmit and receive

power-down can be set independently through SW

control. Total power-down is achieved by powering

down both the transmitter and receiver.

Note: The serial interface and configuration

registers are not affected by power-down.

In HW mode, both transmitters can also be globally

powered down using the TXPD control pin.

LOOPBACK MODES

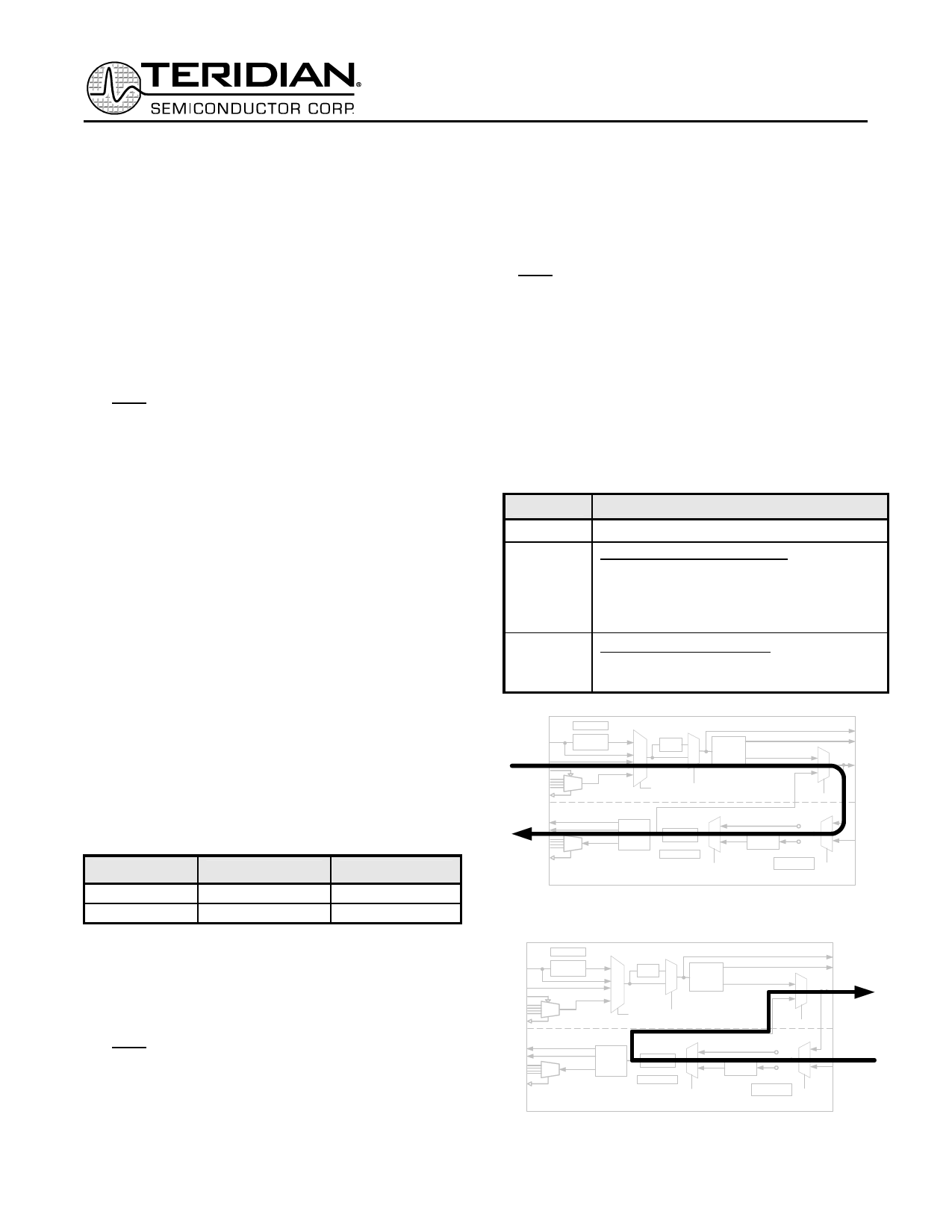

In SW mode, LLBKx and RLBKx bits in the Signal

Control Register are provided to activate the local

and remote loopback modes respectively.

In HW mode, the LPBKx pins can be used to

activate local and remote analog loopback modes as

shown in the table below.

LPBK pin

Low

Float

High

Analog Loopback Mode

Normal operation

Remote (analog) Loopback:

Recovered receive clock and data

looped back directly to the transmit

driver. The CMI decoder and most of

transmit path is bypassed.

Local (analog) Loopback:

Transmit clock and data looped back to

receiver at the analog media interface.

SIxDP/N

SIxCKP/N

PIxCK

PIx[3:0]D

PTOxCK

SOxCKP/N

SOxDP/N

POx[3:0]D

POxCK

Lock Detect

Tx CDR

EACH CHANNEL: Tx

FIFO

CMI

Encoder

PMOD, SMOD[1:0], PAR

ECLxP/N

TXxCKP/N

CMIxP/N

RLBK

CMI

Decoder

Rx CDR

Lock Detect

CMI

EACH CHANNEL: Rx

Adaptive

Eq.

LOS Detect

LLBK

Figure 6: Local (Analog) Loopback

RXxP/N

SIxDP/N

SIxCKP/N

PIxCK

PIx[3:0]D

PTOxCK

SOxCKP/N

SOxDP/N

POx[3:0]D

POxCK

Lock Detect

Tx CDR

EACH CHANNEL: Tx

FIFO

CMI

Encoder

PMOD, SMOD[1:0], PAR

ECLxP/N

TXxCKP/N

CMIxP/N

RLBK

CMI

Decoder

Rx CDR

Lock Detect

CMI

Adaptive

Eq.

LOS Detect

LLBK

EACH CHANNEL: Rx

Figure 7: Remote (Analog) Loopback

RXxP/N

Page: 7 of 42

2006 Teridian Semiconductor Corporation

Rev. 2.4