8405201XA 查看數據表(PDF) - Intersil

零件编号

产品描述 (功能)

比赛名单

8405201XA Datasheet PDF : 35 Pages

| |||

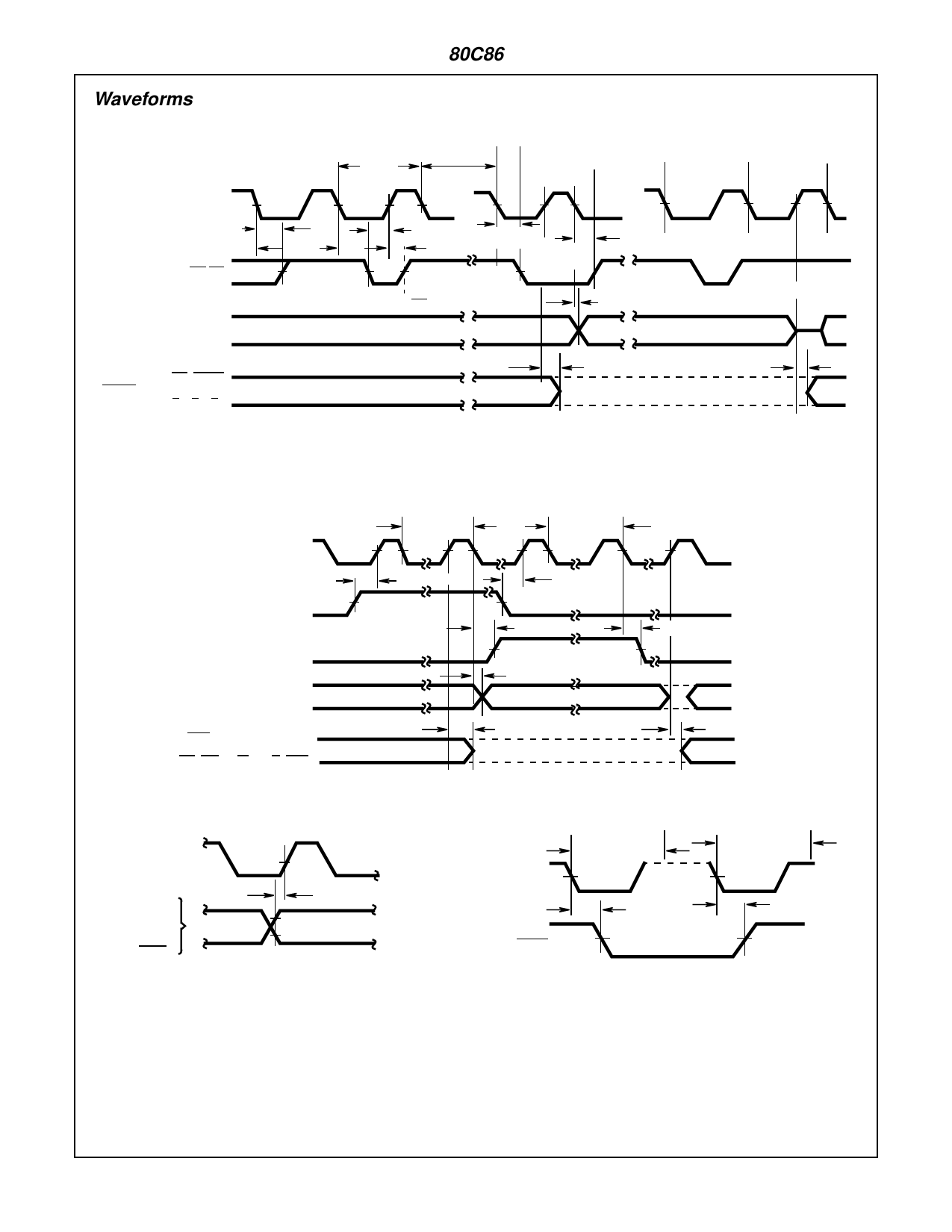

Waveforms (Continued)

80C86

ANY

CLK

CYCLE

>0-CLK

CYCLES

CLK

TCLGH

RQ/GT

(44)

(1)

TCLCL

PREVIOUS GRANT

TGVCH (14) TCLGL

TCHGX (15) (43) PULSE 2

80C86 GT

PULSE 1

COPROCESSOR

RQ

TCLGH (44)

TCLAZ (25)

PULSE 3

COPROCESSOR

RELEASE

AD15-AD0

80C86

COPROCESSOR

RD, LOCK

BHE/S7, A19/S0-A16/S3

S2, S1, S0

TCHSZ (26)

TCHSV (21)

(SEE NOTE)

NOTE: The coprocessor may not drive the busses outside the region shown without risking contention.

FIGURE 9. REQUEST/GRANT SEQUENCE TIMING (MAXIMUM MODE ONLY)

CLK

HOLD

HLDA

AD15-AD0

BHE/S7, A19/S6-A16/S3

RD, WR, M/IO, DT/R, DEN

≥ 1CLK

CYCLE

1 OR 2

CYCLES

THVCH (13)

THVCH (13)

TCLHAV (36)

80C86

TCLAZ (19)

COPROCESSOR

TCHSZ (20)

TCLHAV (36)

80C86

TCHSV (21)

FIGURE 10. HOLD/HOLD ACKNOWLEDGE TIMING (MINIMUM MODE ONLY)

CLK

(13)

NMI

TINVCH (SEE NOTE)

INTR SIGNAL

TEST

NOTE: Setup requirements for asynchronous signals only to guar-

antee recognition at next CLK.

FIGURE 11. ASYNCHRONOUS SIGNAL RECOGNITION

CLK

LOCK

ANY CLK CYCLE

TCLAV

(23)

ANY CLK CYCLE

TCLAV

(23)

FIGURE 12. BUS LOCK SIGNAL TIMING (MAXIMUM MODE

ONLY)

3-166