ICD2025 查看數據表(PDF) - Cypress Semiconductor

零件编号

产品描述 (功能)

比赛名单

ICD2025 Datasheet PDF : 7 Pages

| |||

ICD2025

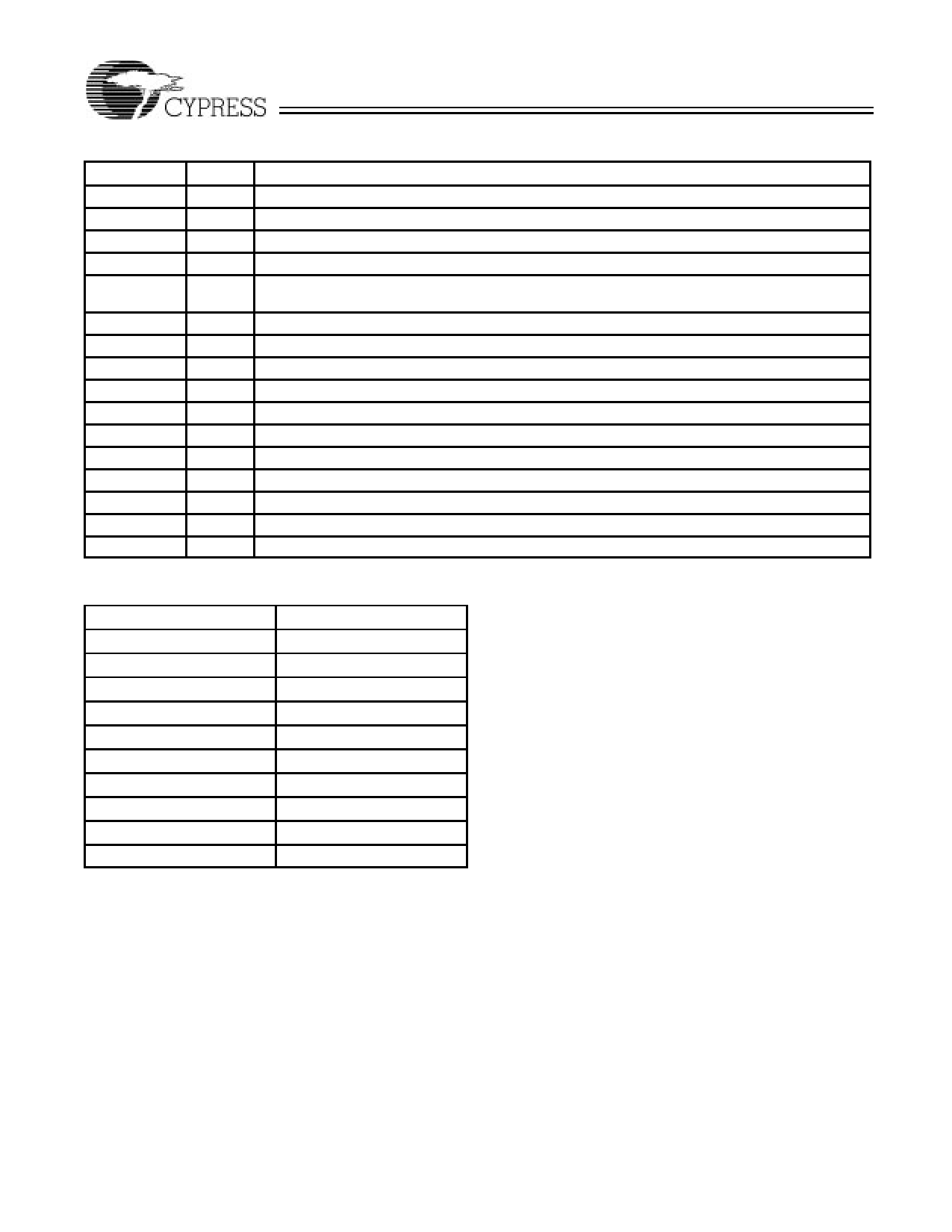

Pin Summary

Name

SYSBUS

SYSCLK

OE

GND

fREF/

XTALIN[1]

XTALOUT[1]

C0

S0

S1

C1

C2

S2

VDD

C3

CPUCLK

AVDD

Number

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

Description

Buffered 14.31818 MHz crystal output (z)

System clock output (see Table 2)

Output Enable threeĆstates output when signal is LO. (pin has internal pullĆup)

Ground

Reference Oscillator input for all internal phaseĆlocked loops (nominally from a parallelĆresonant

14.31818 MHz crystal). Optionally PC System Bus Clock.

Oscillator output to a reference crystal.

CPUCLK Select signalĊBit 0 (internal pullĆup)

SYSCLK Clock Select signalĊBit 0 (internal pullĆup)

SYSCLK Select signalĊBit 1 (internal pullĆup)

CPUCLK Select signalĊBit 1 (internal pullĆup)

CPUCLK Select signalĊBit 2 (internal pullĆup)

SYSCLK Select signalĊBit 2 (internal pullĆup)

+5V to I/O Ring

CPUCLK Select signalĊBit 3 (internal pullĆdown)

CPU Clock Output (See CPUCLK Selection Table)

+5V to Analog Core

Available Frequencies (MHz)

SYSCLK

CPUCLK

1.843

16.000

3.686

20.000

8.000

25.000

12.000

32.000

18.432

33.333

20.000

40.000

24.000

50.000

32.000

66.667

80.000

100.000

Note:

1. For best accuracy, use a parallelĆresonant crystal, assume CLOAD = 17

pF.

2