SAKC505L 查看數據表(PDF) - Infineon Technologies

零件编号

产品描述 (功能)

比赛名单

SAKC505L Datasheet PDF : 85 Pages

| |||

C505L

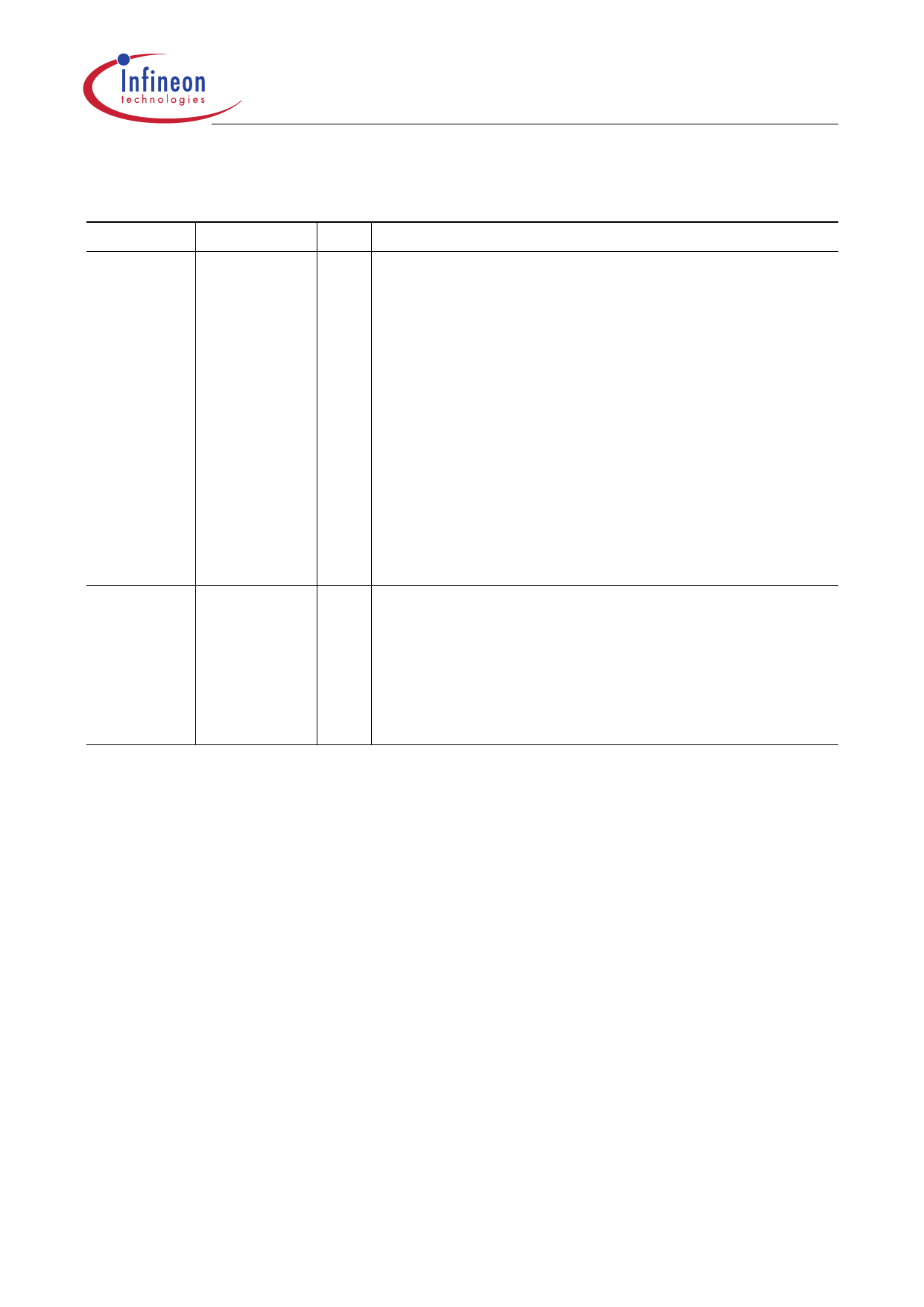

Table 1

Pin Definitions and Functions (cont’d)

Symbol

Pin Number I/O*) Function

P2.7-P2.0 53-60

I/O Port 2

is a an 8-bit quasi-bidirectional I/O port with internal pullup

resistors. Port 2 pins that have a 1 written to them are pulled

high by the internal pullup resistors, and in that state can be

used as inputs. As inputs, port 2 pins being externally pulled

low will source current (IIL, in the DC characteristics)

because of the internal pullup resistors. Port 2 emits the

high-order address byte during fetches from external

program memory and during accesses to external data

memory that use 16-bit addresses (MOVX @DPTR). In this

application it uses strong internal pullup transistors when

issuing 1s. During accesses to external data memory that

use 8-bit addresses (MOVX @Ri), port 2 issues the

contents of the P2 special function register and uses only

the internal pullup resistors.

P0.7-P0.0 61-68

I/O Port 0

is an 8-bit open-drain bidirectional I/O port. Port 0 pins that

have a 1 written to them float, and in that state can be used

as high-impendance inputs. Port 0 is also the multiplexed

low-order address and data bus during accesses to external

program or data memory. In this application it uses strong

internal pullup transistors when issuing 1s.

*) I = Input

O = Output

Data Sheet

10

06.99