M74HC164 查看數據表(PDF) - STMicroelectronics

零件编号

产品描述 (功能)

比赛名单

M74HC164 Datasheet PDF : 13 Pages

| |||

M74HC164

8 BIT SIPO SHIFT REGISTER

s HIGH SPEED :

fMAX = 62MHz (TYP.) at VCC = 6V

s LOW POWER DISSIPATION:

ICC =4µA(MAX.) at TA=25°C

s HIGH NOISE IMMUNITY:

) VNIH = VNIL = 28 % VCC (MIN.)

t(s s SYMMETRICAL OUTPUT IMPEDANCE:

|IOH| = IOL = 4mA (MIN)

uc s BALANCED PROPAGATION DELAYS:

d tPLH ≅ tPHL

ro s WIDE OPERATING VOLTAGE RANGE:

P VCC (OPR) = 2V to 6V

s PIN AND FUNCTION COMPATIBLE WITH

te 74 SERIES 164

ole DESCRIPTION

s The M74HC164 is an high speed CMOS 8 BIT

b SIPO SHIFT REGISTER fabricated with silicon

O gate C2MOS technology.

- The M74HC164 is an 8 bit shift register with serial

t(s) data entry and an output from each of the eight

stages. Data is entered serially through one of two

c inputs (A or B), either of these inputs can be used

u as an active high enable for data entry through the

d other input. An unused input must be high, or both

ro inputs connected together. Each low-to-high

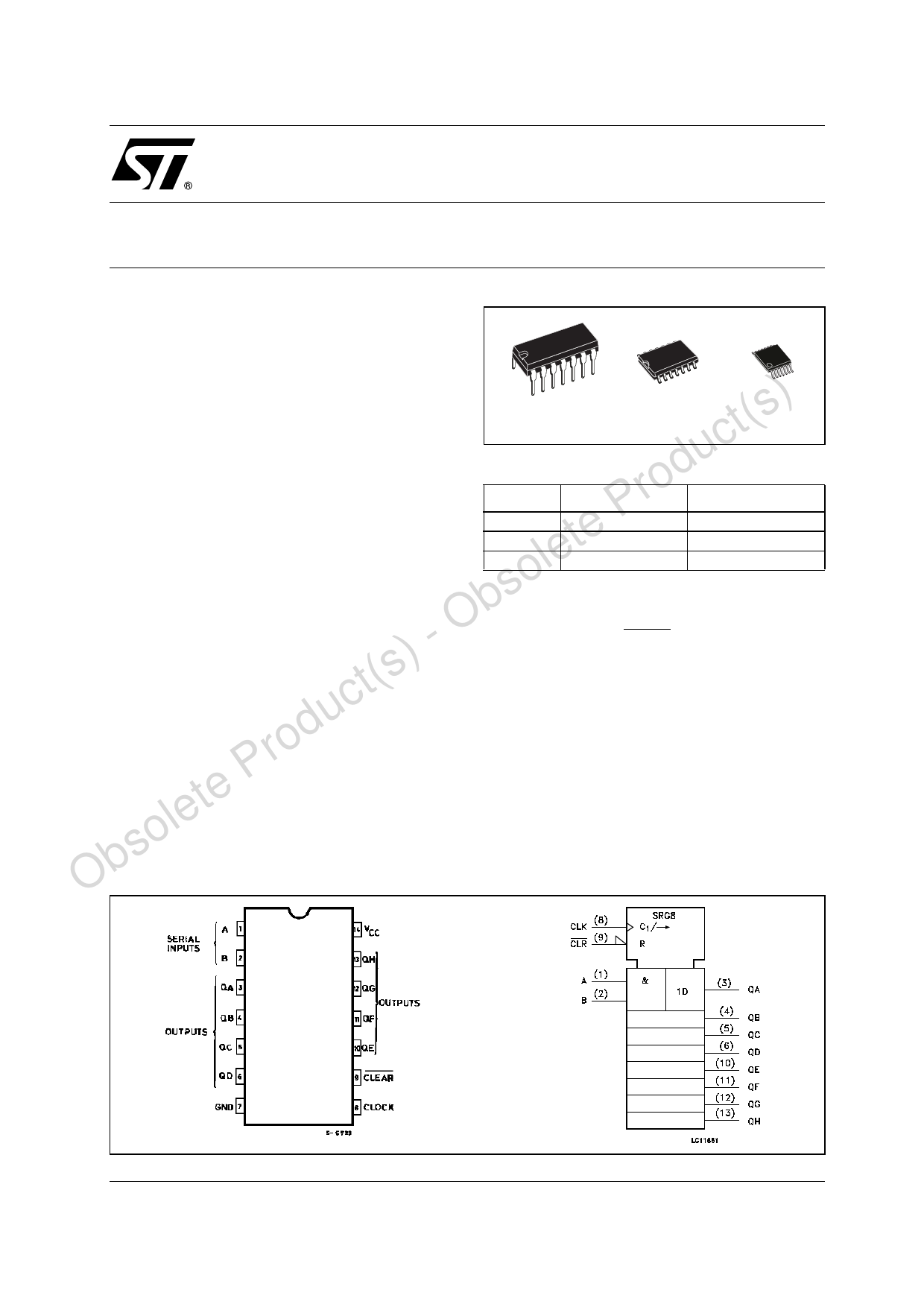

DIP

SOP

TSSOP

ORDER CODES

PACKAGE

TUBE

DIP

SOP

TSSOP

M74HC164B1R

M74HC164M1R

T&R

M74HC164RM13TR

M74HC164TTR

transition on the clock inputs shifts data one place

to the right and enters into QA the logic NAND of

the two data inputs (A x B), the data that existed

before the rising clock edge. A low level on the

clear input overrides all other inputs and clears the

register asynchronously, forcing all Q outputs low.

All inputs are equipped with protection circuits

against static discharge and transient excess

voltage.

Obsolete P PIN CONNECTION AND IEC LOGIC SYMBOLS

June 2003

1/13