LC865504A 查看數據表(PDF) - SANYO -> Panasonic

零件编号

产品描述 (功能)

比赛名单

LC865504A

LC865504A Datasheet PDF : 19 Pages

| |||

LC865520A/16A/12A/08A/04A

(11) Interrupt system

- 13-source 10-vectored interrupts :

1. External interrupt INT0 (include watchdog timer)

2. External interrupt INT1

3. External interrupt INT2, Timer/counter T0L (Lower 8-bit)

4. External interrupt INT3, Base timer

5. Timer/counter T0H (Upper 8-bit)

6. Timer T1L, Timer T1H

7. Serial-interface SIO0

8. Serial-interface SIO1

9. AD converter

10. Port 0

- Built-in Interrupt Priority control register

Microcomputer allows 3 levels of interrupt; low level, high level, and highest level of multiplex interrupt. It can

specify a low level or a high level interrupt priority from INT2/T0L through port 0

(i.e. the above interrupt number from three through ten). It can also specify a low level or the highest level interrupt

priority to INT0 and INT1.

(12) Subroutine stack levels

- 128 levels (Max.): Stack area included in RAM area

(13) Multiplication and division

16-bit × 8-bit (7 instruction cycle times)

16-bit / 8-bit (7 instruction cycle times)

(14) 3 oscillation circuits

- On-chip RC oscillation circuit using for the system clock.

- On-chip CR oscillation circuit using for the system clock.

- On-chip crystal oscillation circuit using for the system clock and for time-base clock.

(15) Standby function

- HALT mode function

The HALT mode is used to reduce power dissipation. In this operation mode, program execution is stopped. This

operation mode can be released by interrupt request signals or the initial system reset request signal.

- HOLD mode function

The HOLD mode is used to freeze all the oscillations;

RC (internal), CR and Crystal oscillations. This mode can be released by the following operations.

• Reset terminal ( RES ) set to Low level

• P70/INT0/T0IN, P71/INT1/T0IN terminals set to assigned level (programmable)

• Port 0 terminal/terminals set to Low level (programmable)

(16) Factory shipment

• DIP42S, QFP48E delivery form

(17) Development support tools

Evaluation (EVA) chip : LC866096

EPROM version

: LC86E5420

One time version

: LC86P5420

Emulator

: EVA-86000 + ECB867100 (Evaluation chip board) + POD865400 (POD)

Notice for use

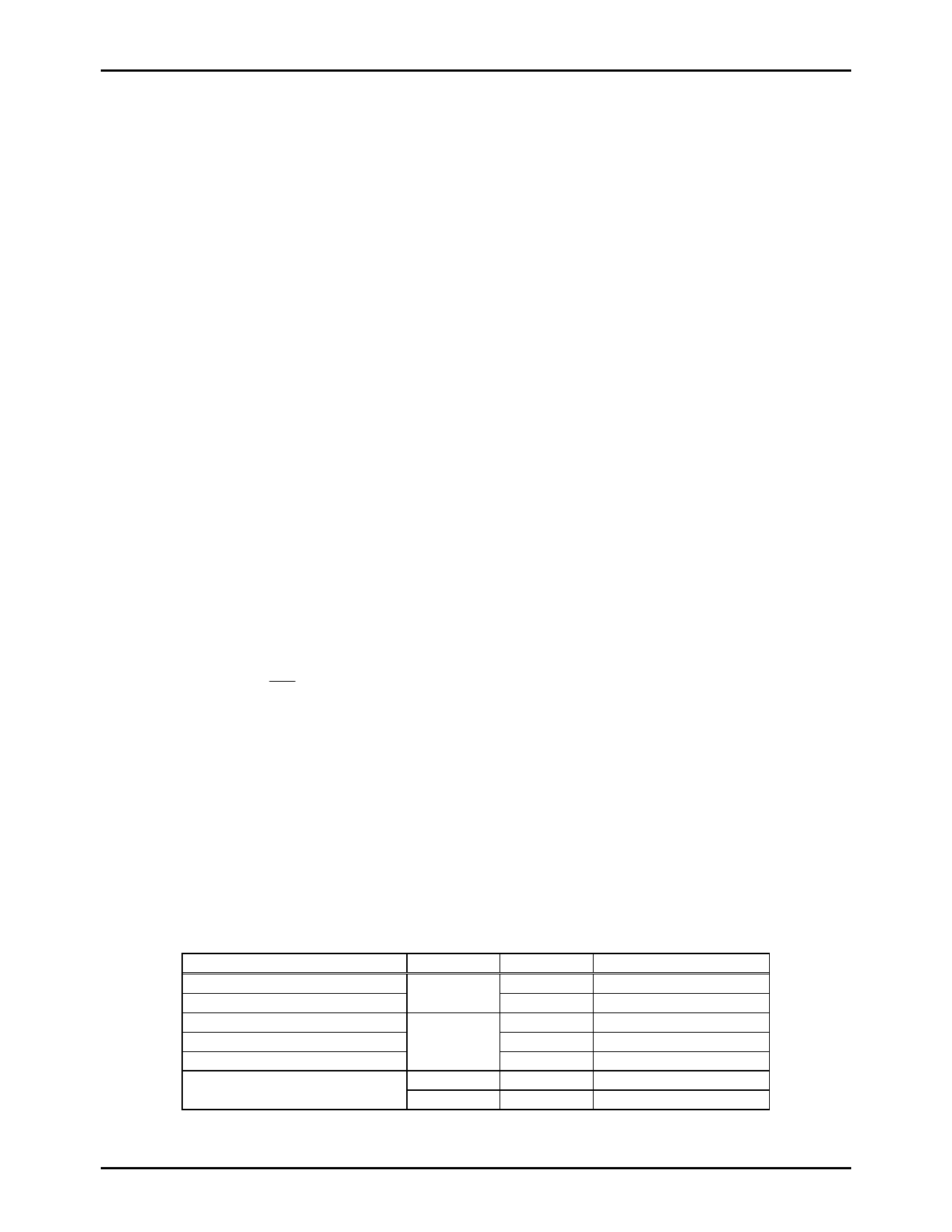

1. Follow the under table.

Frequency range of the system clock Voltage range Clock Divider

15kHz to 30kHz

4.5V to 6.0V

1/1

30kHz to 6MHz

1/1,1/2

15kHz to 30kHz

2.5V to 6.0V

1/1

30kHz to 1.5MHz

1/1,1/2

1.5MHz to 3MHz

1/2

Internal RC oscillation

4.5V to 6.0V 1/1,1/2

2.5V to 6.0V

1/2

Note

Can not use 1/2 divider

Can not use 1/2 divider

Can not use 1/1 divider

Can not use 1/1 divider

3/19