82C84A 查看數據表(PDF) - Renesas Electronics

零件编号

产品描述 (功能)

比赛名单

82C84A Datasheet PDF : 13 Pages

| |||

82C84A

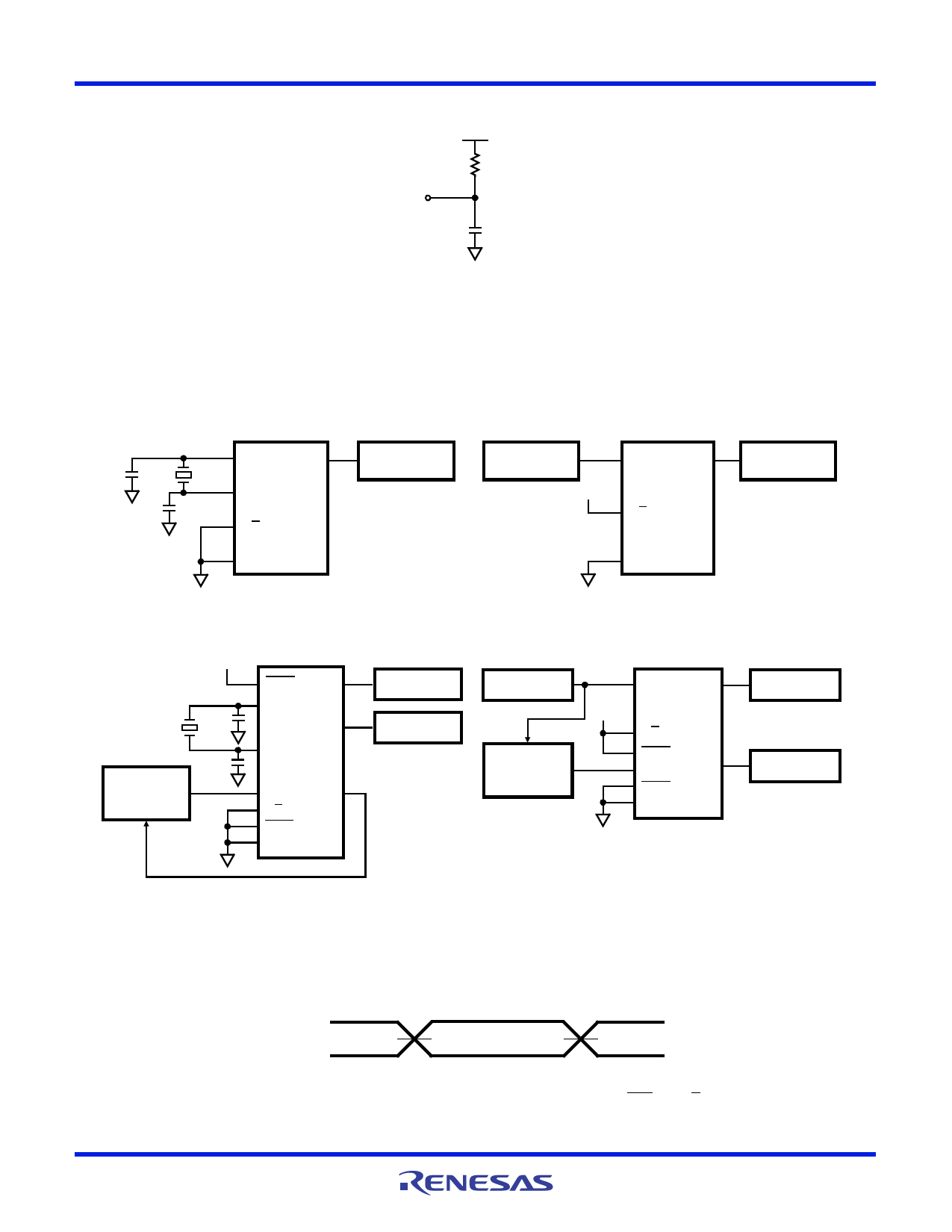

Test Load Circuits

OUTPUT FROM

DEVICE UNDER TEST

2.25V

R = 740 FOR ALL OUTPUTS

EXCEPT CLK

463 FOR CLK OUTPUT

CL

(SEE NOTE 3)

NOTES:

1. CL =100pF for CLK output.

2. CL = 50pF for all outputs except CLK.

3. CL = Includes probe and jig capacitance.

FIGURE 5. TEST LOAD MEASUREMENT CONDITIONS

C1

X1

CLK

LOAD

(SEE NOTE 1)

PULSE

GENERATOR

EF1

CLK

LOAD

(SEE NOTE 1)

X2

VCC

C2

F/C

F/C

CSYNC

CSYNC

FIGURE 6. TCHCL, TCLCH LOAD CIRCUITS

24MHz

PULSE

GENERATOR

TRIGGER

VCC

C1

C2

AEN1 CLK

X1

READY

X2

RDY2

F/C

AEN2

CSYNC

OSC

LOAD

(SEE NOTE 1)

LOAD

(SEE NOTE 2)

PULSE

GENERATOR

TRIGGER

PULSE

GENERATOR

VCC

EF1

CLK

F/C

AEN1

RDY2 READY

AEN2

CSYNC

LOAD

(SEE NOTE 1)

LOAD

(SEE NOTE 2)

FIGURE 7. TRYLCL, TRYHCH LOAD CIRCUITS

AC Testing Input, Output Waveform

INPUT

VIH + 0.4V

OUTPUT

VOH

1.5V

1.5V

VIL - 0.4V

VOL

NOTE: Input test signals must switch between VIL (maximum) -0.4V and VIH (minimum) +0.4V. RES and F/C must switch between 0.4V

and VCC -0.4V. Input rise and fall times driven at 1ns/V. VIL VIL (max) -0.4V for CSYNC pin. VCC -4.5V and 5.5V.

FN2974 Rev 4.00

Sep 9, 2015

Page 10 of 13