M52791SP 查看數據表(PDF) - Renesas Electronics

零件编号

产品描述 (功能)

比赛名单

M52791SP Datasheet PDF : 14 Pages

| |||

M52791SP/FP

I2C Bus

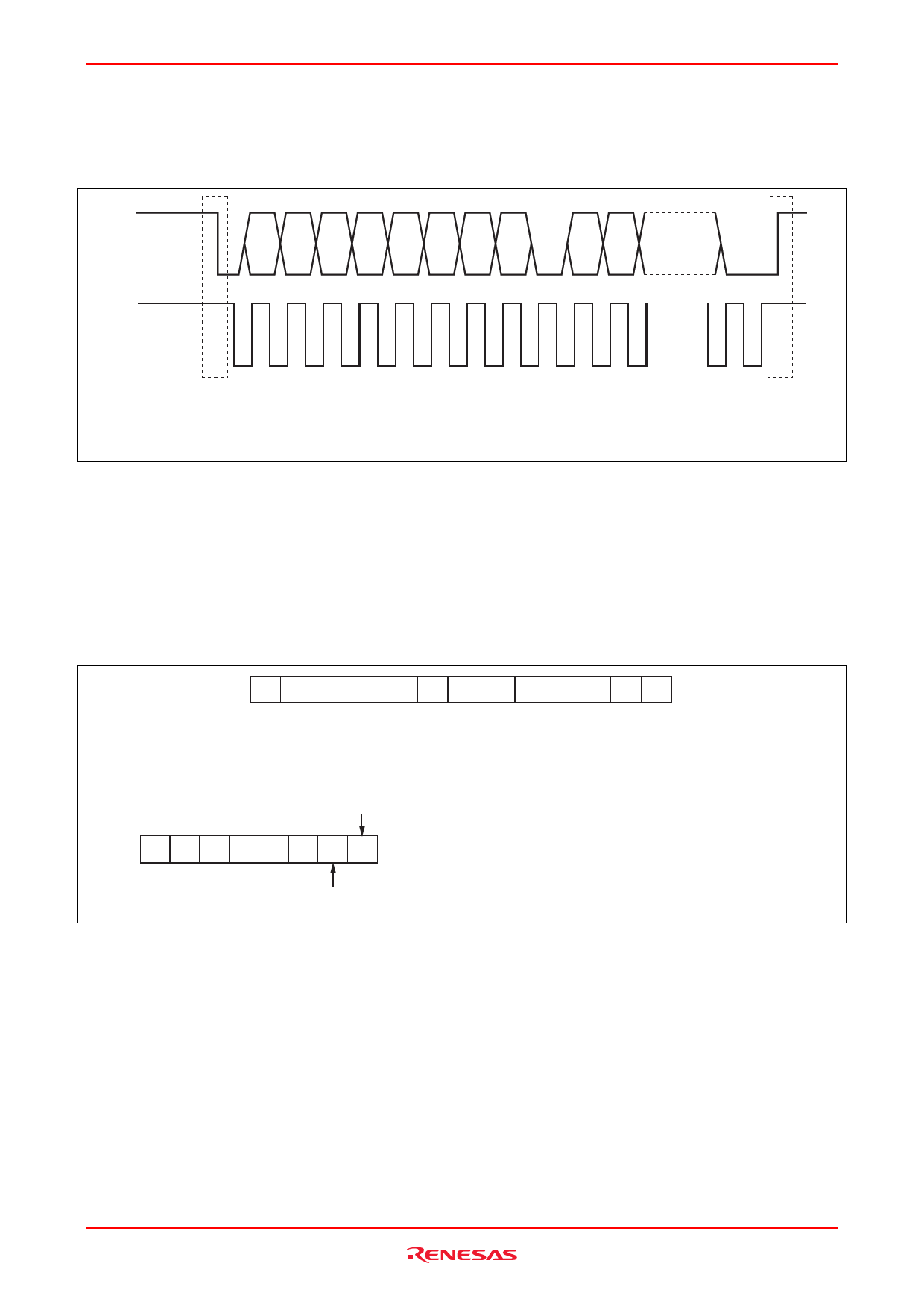

I2C Bus (Inter IC Bus) is multi master bus system developed by PHILIPS. Two wires (SDA-serial data, SCL-serial

clock) realize functions of start, stop, transferring data, synchronization and arbitration. The output stages of device

connected to the bus must have an open drain or open collector in order to perform the wired-AND function.

SDA

A

MSB

SCL

LSB

MSB

Note:

S

12345678912

S: Start condition, a high to low transition of the SDA line while SCL is high

P: Stop condition, a low to high transition of the SDA line while SCL is high

A: Acknowledge

A

LSB

P

9

Every byte put on the SDA line must be 8-bits long. Each byte has to be followed by an acknowledge bit. Data is

transferred with the most significant bit (MSB) first. The data on the SDA line must be stable during the HIGH period

of the clock. The HIGH or LOW state of the data line can only change when the clock signal on the SCL line is LOW.

Control

This IC controls 2-channel switches with 2-byte data (DATA1 and DATA2). Video switches are controlled by DATA1.

Audio switches are controlled by DATA2.

S SLAVE ADDRESS A DATA1 A DATA2 A P

Slave address

S: Start

A: Acknowledge

P: Stop

1 00100X0

R/W bit

Usually "0" (W: Master transmitter transmits to slave receiver)

Possible to select

22 pin High: 1, Low: 0

Rev.2.00 Sep 14, 2006 page 6 of 13