CL3256AQC208-7 查看數據表(PDF) - Clear Logic

零件编号

产品描述 (功能)

比赛名单

CL3256AQC208-7 Datasheet PDF : 14 Pages

| |||

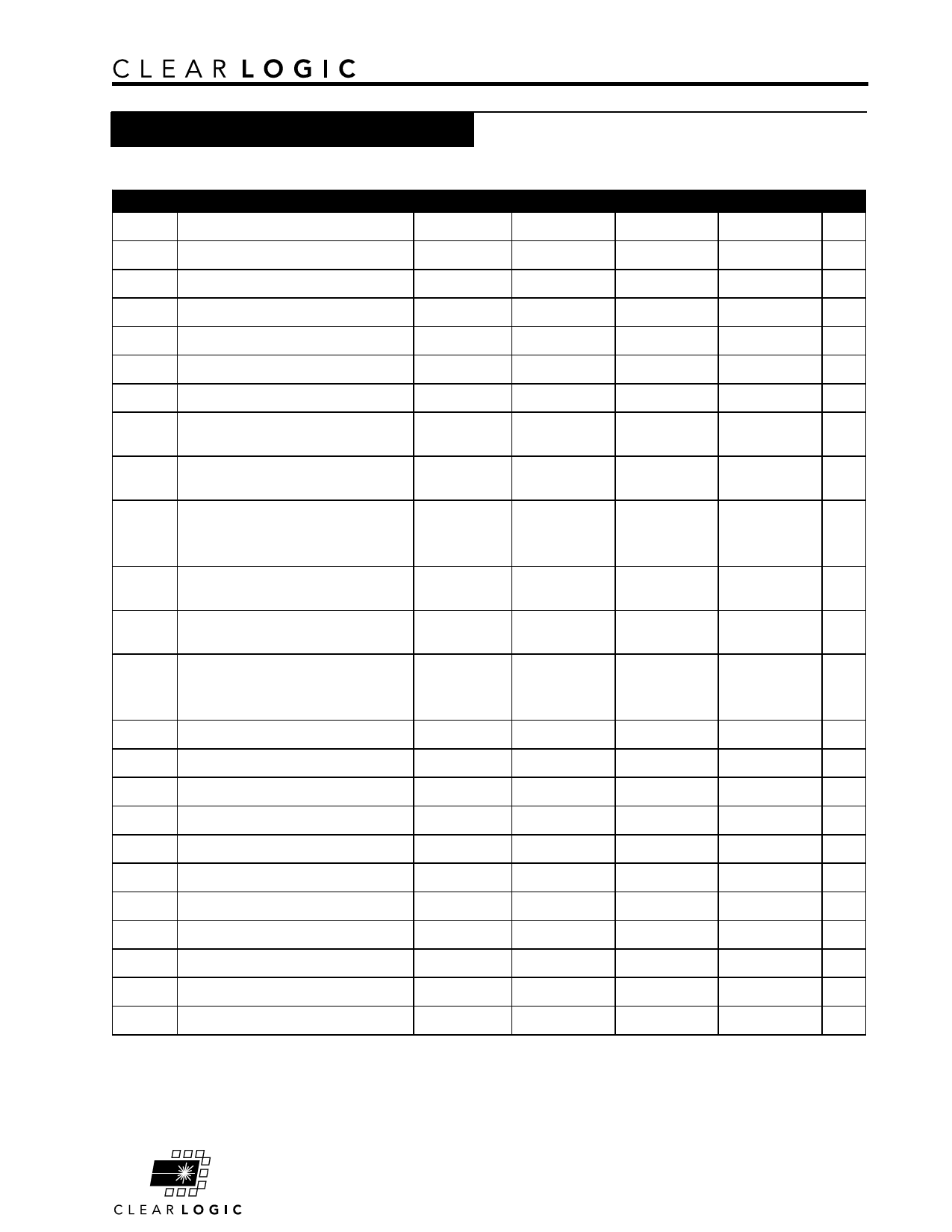

CL3256A Laser Processed Logic Devices

AC Electrical Specifications cont.

Internal Timing Parameters[4]

Speed: -4

Symbol

Parameter

Conditions Min Max

tiN

Input pad and buffer delay

0.3

tIO I/O input pad and buffer delay

0.3

tSEXP Shared expander delay

1.9

tPEXP Parallel expander delay

0.5

tLAD Logic array delay

1.9

tLAC Logic control array delay

1.8

tIOE Internal output enable delay

0.0

tOD1 Output buffer and pad delay

CL = 35 pF

0.3

Slow slew rate = off, VCCIO = 5.0 V

tOD2 Output buffer and pad delay

CL = 35 pF

0.8

Slow slew rate = off, VCCIO = 3.3 V

Output buffer and pad delay

tOD3 Slow slew rate = on,

CL = 35 pF

5.3

VCCIO = 5.0 V or 3.3 V

tZX1

Output buffer enable delay

Slow slew rate = off, VCCIO = 5.0 V

CL = 35 pF

4.0

tZX2 Output buffer enable delay

CL = 35 pF

4.5

Slow slew rate = off, VCCIO = 3.3 V

Output buffer enable delay

tZX3 Slow slew rate = on,

CL = 35 pF

9.0

VCCIO = 5.0 V or 3.3 V

tXZ Output buffer disable delay

CL = 5 pF[3]

4.0

tSU Register setup time

1.4

tH

Register hold time

0.8

tRD Register delay

1.2

tCOMB Combinatorial delay

1.3

tIC

Array clock delay

1.9

tEN Register enable time

1.8

tGLOB Global control delay

1.0

tPRE Register preset time

2.3

tCLR Register clear time

2.3

tLIA LIA delay

0.7

Speed: -5

Min Max

0.3

0.3

2.4

0.6

2.5

2.3

0.0

0.4

0.9

5.4

4.0

4.5

9.0

4.0

0.8

1.0

1.4

1.0

2.3

2.3

0.9

2.6

2.6

0.8

Speed: -6

Min Max Unit

0.3 ns

0.3 ns

2.8 ns

0.5 ns

2.5 ns

2.5 ns

0.2 ns

0.3 ns

0.8 ns

5.3 ns

4.0 ns

4.5 ns

9.0 ns

4.0 ns

1.0

ns

1.7

ns

1.6 ns

1.6 ns

2.7 ns

2.5 ns

1.1 ns

2.3 ns

2.3 ns

1.3 ns

3KA tbl 07A1

Page 11