IDT71V509S66Y 查看數據表(PDF) - Integrated Device Technology

零件编号

产品描述 (功能)

比赛名单

IDT71V509S66Y

IDT71V509S66Y Datasheet PDF : 9 Pages

| |||

IDT71V509

128K X 8 3.3V SYNCHRONOUS SRAM WITH ZBT™ AND FLOW-THROUGH OUTPUT

COMMERCIAL TEMPERATURE RANGE

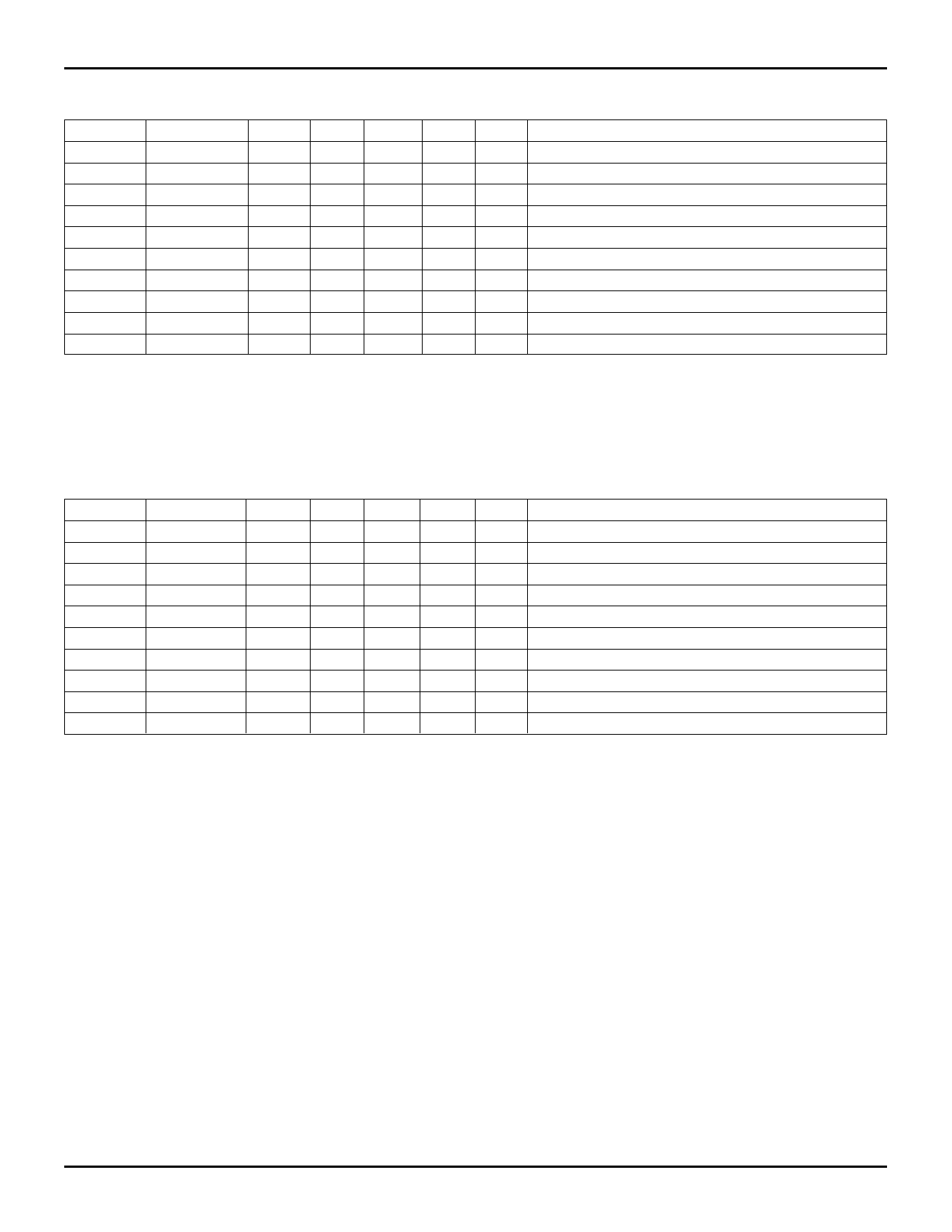

READ OPERATION WITH CHIP SELECT USED

Cycle Address

WE CS CEN OE I/O

n

X

X

H

L

X

?

n+1

X

X

H

L

X

Z

n+2

A2

H

L

L

X

Z

n+3

X

X

H

L

L

D2

n+4

A4

H

L

L

X

Z

n+5

X

X

H

L

L

D4

n+6

X

X

H

L

X

Z

n+7

A7

H

L

L

X

Z

n+8

X

X

H

L

L

D7

n+9

X

X

H

L

X

Z

H = High; L = Low; X = Don’t Care; ? = Don’t Know; Z = High Impedance

Comments

Deselected

Deselected

Address and Control meet setup

Deselected, Contents of Address A2 Read Out

Address and Control meet setup

Deselected, Contents of Address A4 Read Out

Deselected

Address and Control meet setup

Deselected, Contents of Address A7 Read Out

Deselected

3618 tbl 06

WRITE OPERATION WITH CHIP SELECT USED

Cycle Address

WE CS CEN OE I/O

n

X

X

H

L

X

?

n+1

X

X

H

L

X

Z

n+2

A2

L

L

L

X

Z

n+3

X

X

H

L

X

D2

n+4

A4

L

L

L

X

Z

n+5

X

X

H

L

X

D4

n+6

X

X

H

L

X

Z

n+7

A7

L

L

L

X

Z

n+8

X

X

X

L

X

D7

n+9

X

X

X

L

X

Z

H = High; L = Low; X = Don’t Care; ? = Don’t Know; Z = High Impedance

Comments

Deselected

Deselected

Address and Control meet setup

Deselected, New Data Drives SRAM Inputs

Address and Control meet setup

Deselected, New Data Drives SRAM Inputs

Deselected

Address and Control meet setup

Deselected, New Data Drives SRAM Inputs

Deselected

3618 tbl 07

11.3

5