HS-82C85RH(2000) 查看數據表(PDF) - Intersil

零件编号

产品描述 (功能)

比赛名单

HS-82C85RH Datasheet PDF : 16 Pages

| |||

HS-82C85RH

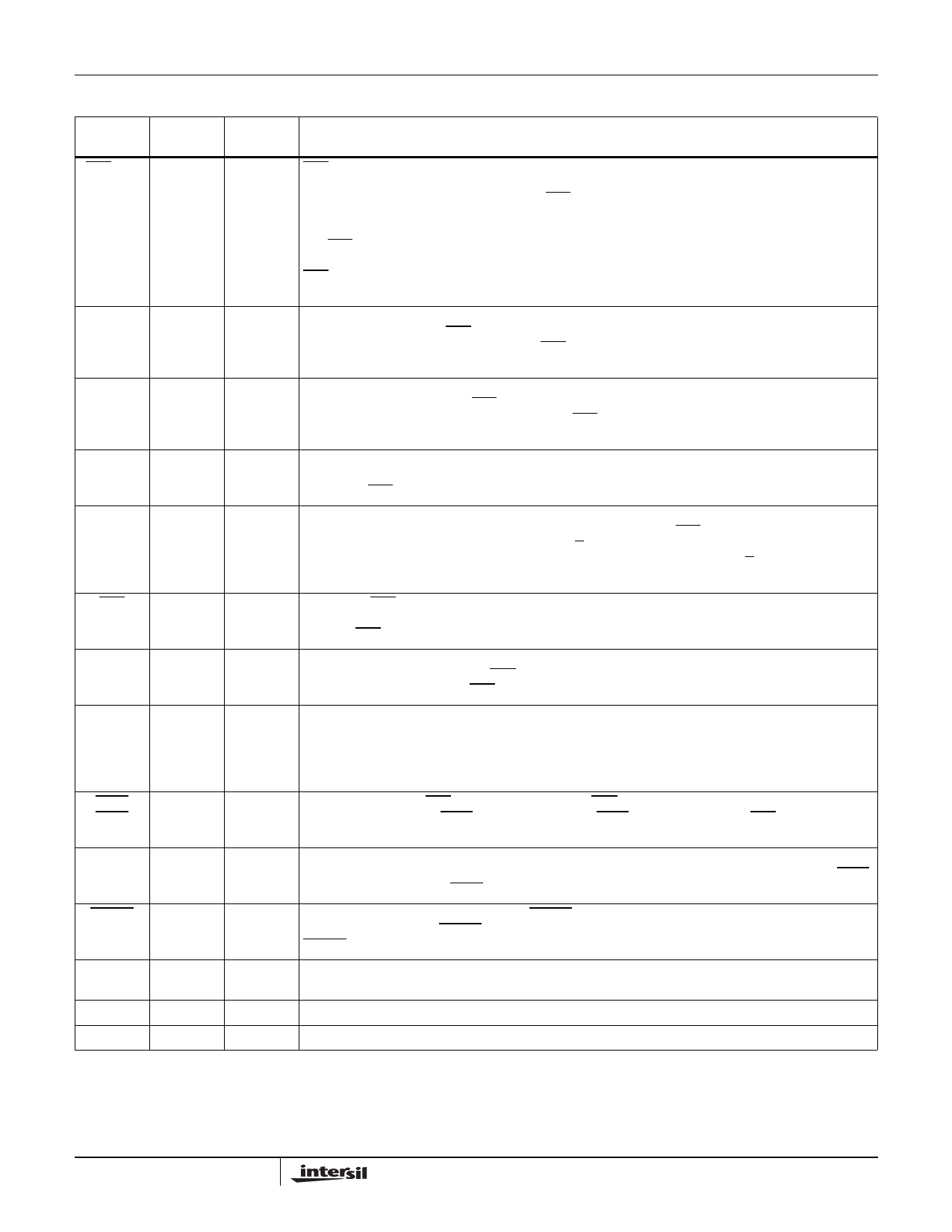

Pin Descriptions (Continued)

PIN

PIN

NUMBER TYPE

DESCRIPTION

SLO/FST

12

I

SLO/FST is a level-triggered input. When HIGH, the CLK and CLK50 outputs run at the maximum

frequency (crystal or EFI frequency divided by 3). When LOW, CLK and CLK50 frequencies are equal to

the crystal or EFI frequency divided by 768. SLO/FST mode changes are internally synchronized to

eliminate glitches on the CLK and CLK50. START and STOP control of the oscillator or EFI is available

in either the SLOW or FAST frequency modes.

The SLO/FST input must be held LOW for at least 195 OSC/EFI clock cycles before it will be recognized.

This eliminates unwanted frequency changes which could be caused by glitches or noise transients. The

SLO/FST input must be held HIGH for at least 6 OSC/EFI clock pulses to guarantee a transition to FAST

mode operation.

CLK

8

O

PROCESSOR CLOCK: CLK is the clock output used by the HS-80C86RH processor and other

peripheral devices. When SLO/FST is high, CLK has an output frequency which is equal to the crystal or

EFI input frequency divided by three. When SLO/FST is low, CLK has an output frequency which is equal

to the crystal or EFI input frequency divide by 768. CLK has a 33% duty cycle.

CLK50

10

O

50% DUTY CYCLE CLOCK: CLK50 is an auxiliary clock with a 50% duty cycle and is synchronized to

the falling edge of CLK. When SLO/FST is high, CLK50 has an output frequency which is equal to the

crystal or EFI input frequency divided by 3. When SLO/FST is low, CLK50 has an output frequency equal

to the crystal or EFI input frequency divided by 768.

PCLK

2

O

PERIPHERAL CLOCK: PCLK is a peripheral clock signal whose output frequency is equal to the crystal

or EFI input frequency divided by six and has a 50% duty cycle. PCLK frequency is unaffected by the

state of the SLO/FST input.

OSC

18

O

OSCILLATOR OUTPUT: OSC is the output of the internal oscillator circuitry. Its frequency is equal to

that of the crystal oscillator circuit. OSC is unaffected by the state of the SLO/FST input.

When the HS-82C85RH is in the crystal mode (F/C LOW) and a STOP command is issued, the OSC

output will stop in the HIGH state. When the HS-82C85RH is in the EFI mode (F/C HIGH), the oscillator

(if operational) will continue to run when a STOP command is issued and OSC remains active.

RES

17

I

RESET IN: RES is an active LOW signal which is used to generate RESET. The HS-82C85RH provides

a Schmitt trigger input so that an RC connection can be used to establish the power-up reset of proper

duration. RES starts crystal oscillator operation.

RESET

16

O

RESET: RESET is an active HIGH signal which is used to reset the HS-80C86RH processor. Its timing

characteristics are determined by RES. RESET is guaranteed to be HIGH for a minimum of 16 CLK

pulses after the rising edge of RES.

CSYNC

1

I

CLOCK SYNCHRONIZATION: CSYNC is an active HIGH signal which allows multiple HS-82C85RHs to

be synchronized to provide multiple in-phase clock signals. When CSYNC is HIGH, the internal counters

are reset and force CLK, CLK50 and PCLK into a HIGH state. When CSYNC is LOW, the internal

counters are allowed to count and the CLK, CLK50 and PCLK outputs are active. CSYNC must be

externally synchronized to EFI.

AEN1

3

AEN2

7

I

ADDRESS ENABLE: AEN is an active LOW signal. AEN serves to qualify its respective Bus Ready

I

Signal (RDY1 or RDY2). AEN1 validates RDY1 while AEN2 validates RDY2. Two AEN signal inputs are

useful in system configurations which permit the processor to access two Multi-Master System Buses.

RDY1

4

RDY2

6

I

BUS READY: (Transfer Complete). RDY is an active HIGH signal which is an indication from a device

I

located on the system data bus that data has been received, or is available. RDY1 is qualified by AEN1

while RDY2 is qualified by AEN2.

ASYNC

21

I

READY SYNCHRONIZATION SELECT: ASYNC is an input which defines the synchronization mode of

the READY logic. When ASYNC is LOW, two stages of READY synchronization are provided. When

ASYNC is left open or HIGH a single stage of READY synchronization is provided.

READY

5

O

READY: READY is an active HIGH signal which is used to inform the HS-80C86RH that it may conclude

a pending data transfer.

GND

9

I

Ground

VDD

24

I

+5V power supply

3