ST16 查看數據表(PDF) - STMicroelectronics

零件编号

产品描述 (功能)

比赛名单

ST16 Datasheet PDF : 21 Pages

| |||

ST16-19RFRDCS

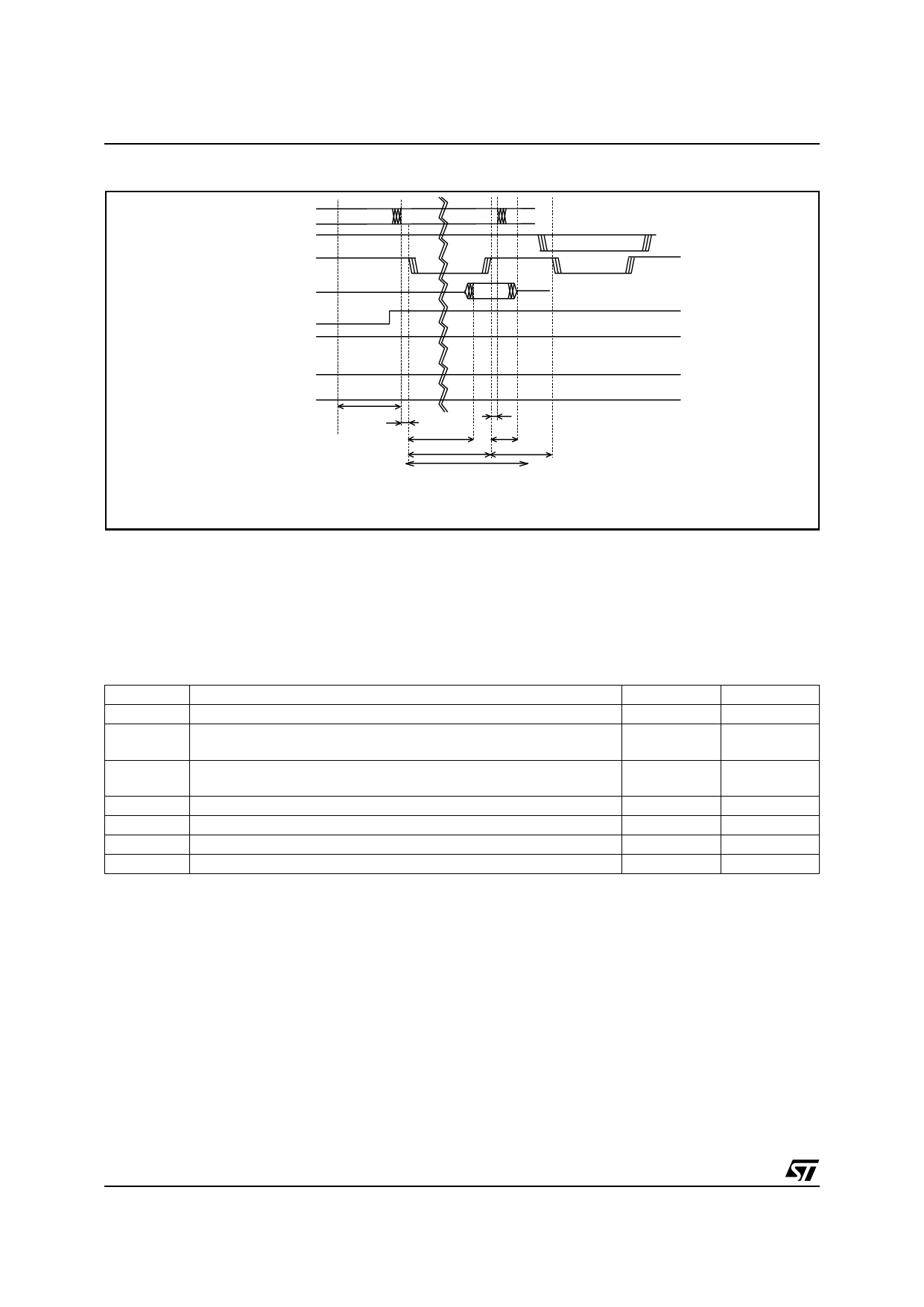

Figure 3 FPGA read access chronogram for last byte

Mic_Ctrl_Data

Mic_RW

Mic_Strb_b

Mic_Data(7:0)

Rx_fifo_empty

Rx_irq_eof

Tx_start

Tx_fifo_empty

t0 t1

t2

t5

t6

t3

t4

Acquisition of the last byte

FSD_CHIPSET_B/0104VP2

Before sending the last byte the FPGA takes the Rx_fifo_empty line high to indicate to the MCU that this

is the last data.

1.3.5 MCU interface timings

The following board provides interface timings (cf previous chronogram)

Table 1 : Interface timing

Timing

t0

t1

t2

t3

t4

t5

t6

Parameter

Rx_irq_eof to Mic_Strb_b Transition

Mic_Ctrl_Data, Mic_RW (and Mic_Data in writing) Setup Time before

Mic_Strb_b Low Transition

Mic_Ctrl_Data, Mic_RW (and Mic_Data in writing) Hold Time before

Mic_Strb_b High Transition

Mic_Strb_b Width Low (Activ)

Mic_Strb_b Width High (Inactiv)

Mic_Strb_b Activ to Valid Data in Reading

Mic_Strb_b Inactiv to Tri-States Data in Reading

Min. (ns)

0

0

0

240

80

Max. (ns)

240

20

4/15