MX105AP 查看數據表(PDF) - MX-COM Inc

零件编号

产品描述 (功能)

比赛名单

MX105AP Datasheet PDF : 15 Pages

| |||

Tone Detector

6

MX105A PRELIMINARY INFORMATION

4. General Description

The MX105A implements a frequency detector with a phase locked loop (PLL) and a lock detector. The voltage controlled

oscillator (VCO) center frequency, detection bandwidth, loop filter, and detect filter are all independently controlled by

external components.

The MX105A provides a pair of pseudo-sinewave multipliers for splitting the input signal into approximately orthogonal

components. These multipliers are implemented with commutating filters (cyclically sampling filters) which translate an in

band AC input signal to DC. The commutating loop filter is used as the phase detector of the PLL while the commutating

detect filter provides for lock detection. Each pseudo-sinewave has a cyclic form (1 1 0 -1 -1 0) to eliminate low order

harmonic responses. The loop filter produces an error signal, which when applied to the VCO input allows frequency

locking. A limiter between the loop filter output and the VCO input provides tunable control of the detection bandwidth

(BW). Once lock is achieved the detect filter produces a DC value proportional to the input tone amplitude. An internally

generated reference is compared to the detect filter output to determine whether the PLL is locked to an input tone. Once

lock is determined the internal reference is reduced by 50% to minimize output chatter with marginal input signals.

The sampling clocks of the detect filter lag those of the loop filter by 60°. To improve performance, a capacitor (C4) can

be used to phase shift the input to the loop filter by 30°. This shifts all sampling clocks an additional 30° relative to the

input tone to phase align the detect filter sampling clocks with the amplitude peaks of the input tone.

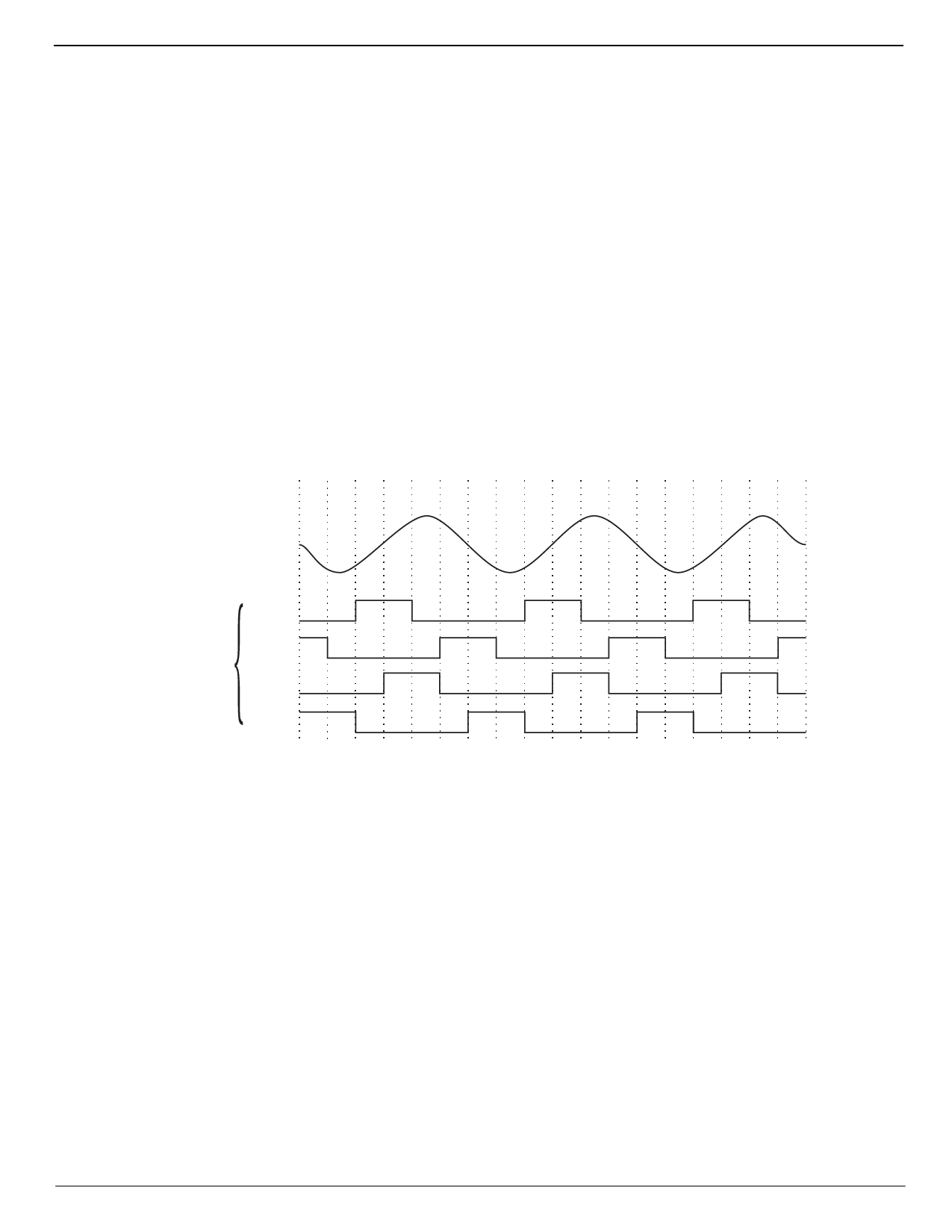

Figure 3 shows the sampling clocks relative to an in band input tone; this figure represents the steady state ‘locked’

condition without C4.

Internal Clock 4 5 6 1 2 3 4 5 6 1 2 3 4 5 6 1 2 3

Segment

Input Tone

C2B

Logic 1

indicates

C2A

sampling

period

C3A

C3B

Figure 3: Sampling Clocks of Commutating Filters

© 1997 MX•COM, INC.

www.mxcom.com Tele: 800 638 5577 910 744 5050 Fax: 910 744 5054

Doc.# 20480133.003

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USA

All trademarks and service marks are held by their respective companies.