29103BRA 查看數據表(PDF) - Intersil

零件编号

产品描述 (功能)

比赛名单

29103BRA Datasheet PDF : 8 Pages

| |||

HM-65262

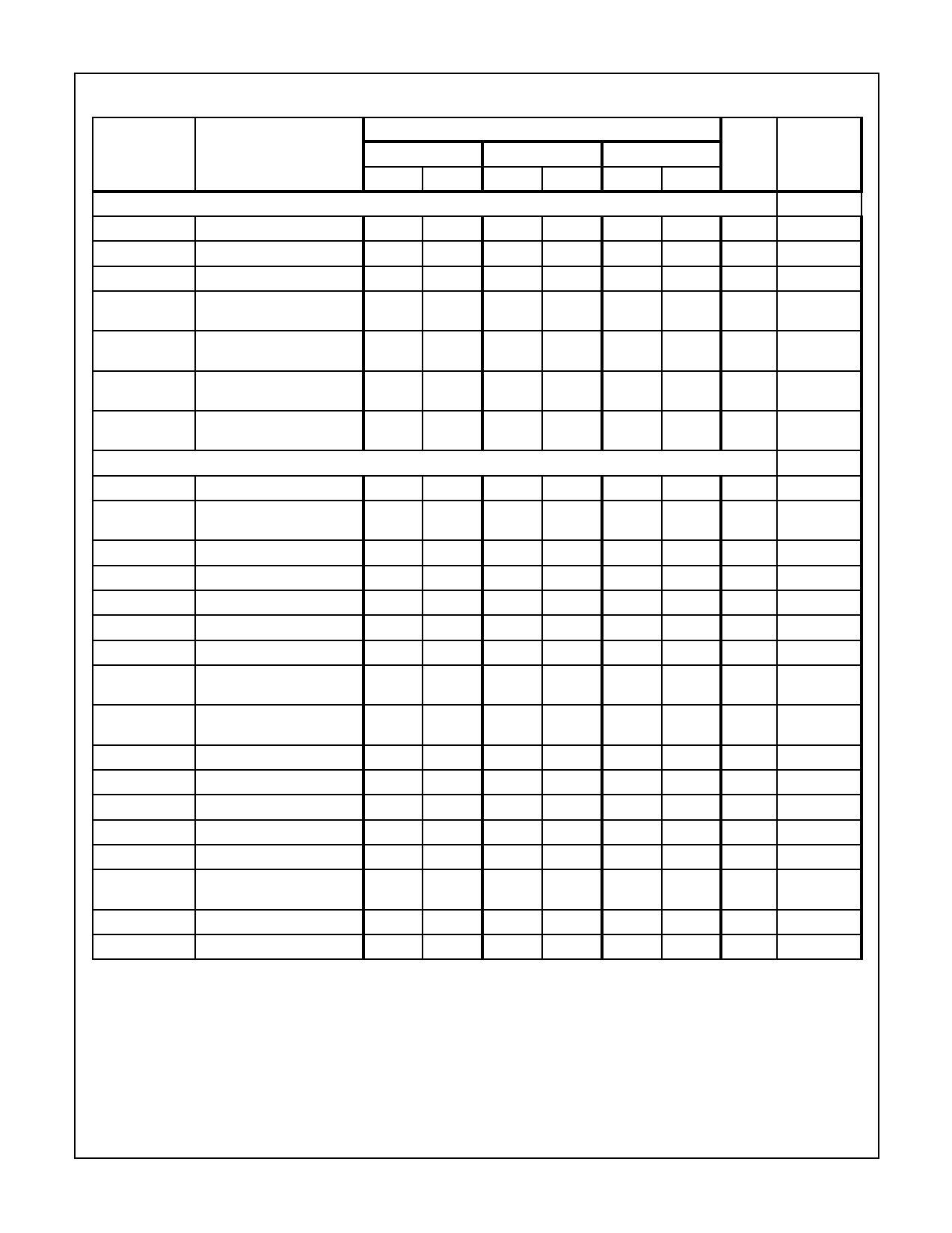

AC Electrical Specifications VCC = 5V ± 10%, TA = -40oC to +85oC (HM-65262B-9, HM-65262-9, HM-65262C-9)

LIMITS

SYMBOL

PARAMETER

HM-65262B-9

MIN

MAX

HM-65262-9

MIN

MAX

HM-65262C-9

MIN

MAX

TEST

UNITS CONDITIONS

READ CYCLE

(1) TAVAX Read/Cycle Time

70

-

85

-

85

-

ns

(Notes 1, 3)

(2) TAVQV Address Access Time

-

70

-

85

-

85

ns (Notes 1, 3)

(3) TELQV Chip Enable Access Time

-

70

-

85

-

85

ns

(Notes 1, 3)

(4) TELQX Chip Enable Output Enable

5

-

5

-

5

-

ns

(Notes 2, 3)

Time

(5) TEHQX Chip Disable Output Hold

5

-

5

-

5

-

ns (Notes 2, 3)

Time

(6) TAXQX Address Invalid Output Hold

5

-

5

-

5

-

ns

(Notes 2, 3)

Time

(7) TEHQZ Chip Enable Output Disable

-

30

-

30

-

30

ns

(Notes 2, 3)

Time

WRITE CYCLE

(8) TAVAX Write Cycle Time

70

-

85

-

85

-

ns

(Notes 1, 3)

(9) TELWH Chip Selection to End of

Write

55

-

65

-

65

-

ns

(Notes 1, 3)

(10) TWLWH Write Enable Pulse Width

40

-

45

-

45

-

ns (Notes 1, 3)

(11) TAVWL Address Setup Time

0

-

0

-

0

-

ns

(Notes 1, 3)

(12) TWHAX Address Hold Time

0

-

0

-

0

-

ns

(Notes 1, 3)

(13) TDVWH Data Setup Time

30

-

35

-

35

-

ns (Notes 1, 3)

(14) TWHDX Data Hold Time

0

-

0

-

0

-

ns

(Notes 1, 3)

(15) TWLQZ Write Enable Output Disable

-

30

-

30

-

30

ns

(Notes 2, 3)

Time

(16) TWHQX Write Disable Output Enable

0

-

0

-

0

-

ns (Notes 2, 3)

Time

(17) TAVWH Address Valid to End of Write 55

-

65

-

65

-

ns

(Notes 1, 3)

(18) TAVEL Address Setup Time

0

-

0

-

0

-

ns

(Notes 1, 3)

(19) TEHAX Address Hold Time

0

-

0

-

0

-

ns (Notes 1, 3)

(20) TAVEH Address Valid to End of Write 55

-

65

-

65

-

ns

(Notes 1, 3)

(21) TELEH Enable Pulse Width

55

-

65

-

65

-

ns

(Notes 1, 3)

(22) TWLEH Write Enable Pulse Setup

40

-

45

-

45

-

ns (Notes 1, 3)

Time

(23) TDVEH Chip Setup Time

30

-

35

-

35

0

ns

(Notes 1, 3)

(24) TEHDX Data Hold Time

0

-

0

-

0

-

ns

(Notes 1, 3)

NOTES:

1. Input pulse levels: 0 to 3.0V; Input rise and fall times: 5ns (max); Input and output timing reference level: 1.5V; Output load: 1 TTL gate

equivalent and CL = 50pF (min) - for CL greater than 50pF, access time is derated by 0.15ns per pF.

2. Tested at initial design and after major design changes.

3. VCC = 4.5 and 5.5V.

4