AD8155 查看數據表(PDF) - Analog Devices

零件编号

产品描述 (功能)

比赛名单

AD8155 Datasheet PDF : 36 Pages

| |||

AD8155

RECEIVERS

The AD8155 receivers incorporate 50 Ω on-chip termination,

ESD protection, and a multizero equalization function capable

of delivering up to 18 dB of boost at 4.25 GHz. The AD8155 can

compensate signal degradation at 6.5 Gbps from over 40 inches

of FR4 backplane trace. The receive path also incorporates a

loss-of-signal (LOS) function that squelches the associated

transmitter when the midband differential voltage falls below a

specified threshold value. Finally, the receivers implement a sign-

swapping option (P/N swap), which allows the user to invert the

sign of the input signal path and eliminates the need for board-

level crossovers in the receive channels.

Input Structure and Allowed Input Levels

The AD8155 tolerates an input common-mode range (meas-

ured with zero differential input) of

VEE + 0.6 V < VICM < VCC + 0.3 V

Typical supply configurations include, but are not limited to,

those listed in Table 9.

Table 9. Typical Input Supply Configurations

Configuration

DVCC

VCC

Low VTTI, AC-Coupled Input

3.3 V − 1.8 V 1.8 V

Single 1.8 V Supply

3.3 V − 1.8 V 1.8 V

3.3 V Core

3.3 V

3.3 V

Single 3.3 V Supply

3.3 V

3.3 V

VTTI

1.6 V

1.8 V

1.8 V

3.3 V

When dc-coupling with LVDS, CML, or ECL signals, it can be

advantageous to operate with split or negative supplies (see the

Applications Information section). In these applications, it is

necessary to observe the maximum voltage ratings between VCC

and VEE and to select supply voltages for VTTO and VTTI in the

range of VCC to VEE to avoid activating the ESD protection

devices.

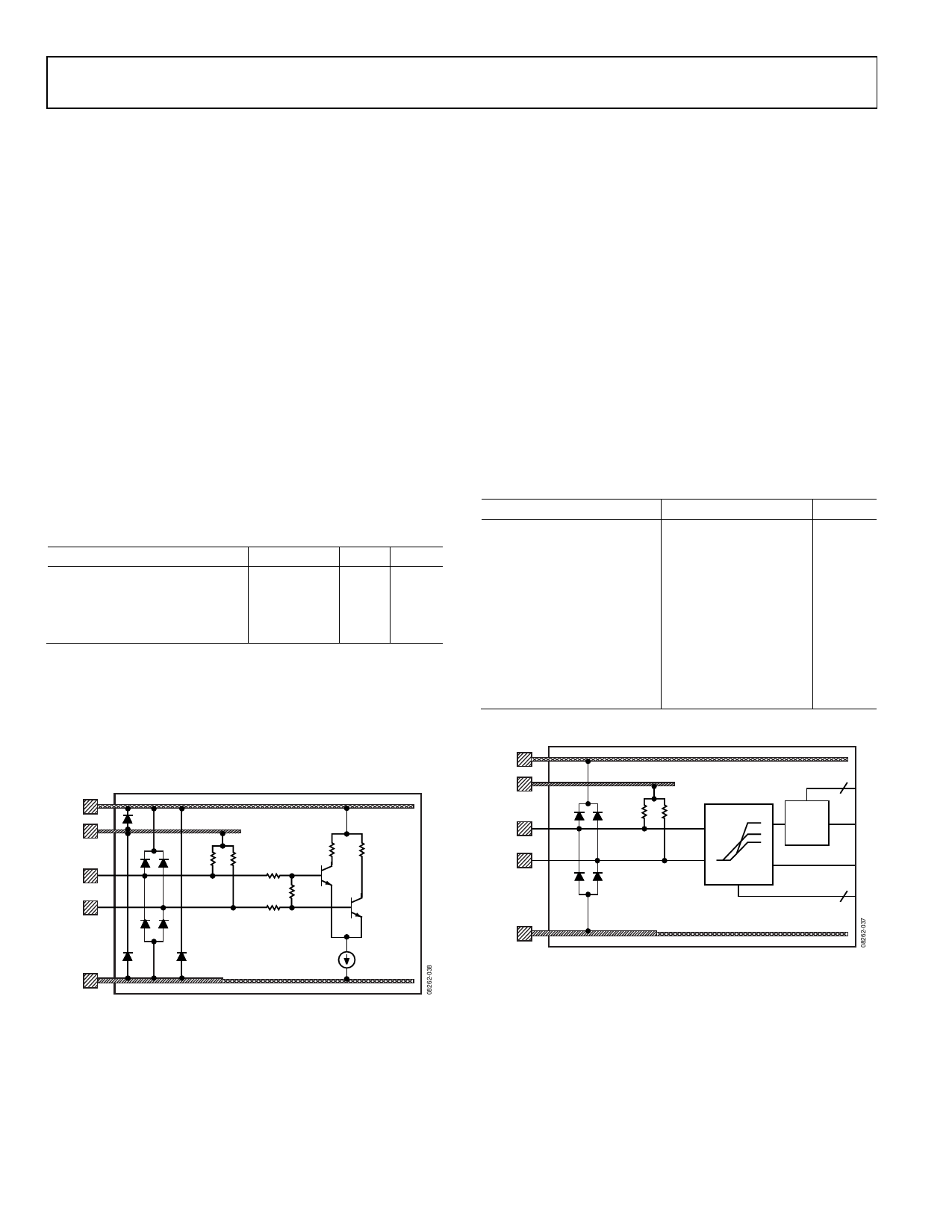

VCC

VTTI

IP_xx

IN_xx

RLN

RLP

RP

RN R1

RL

RL

52Ω

52Ω 750Ω

Q1

R3

1kΩ

Q2

R2

750Ω

I1

VEE

Figure 37. Simplified Receiver Input Structure

Equalizer Settings

Every input lane offers a low power, asynchronous, programma-

ble receive equalizer for NRZ data up to 6.5 Gbps. The pin control

interface allows two levels of receive equalization. Register-based

control allows the user 10 equalizer settings. Register and pin

control boost settings are listed in Table 10. Equalization capa-

bility and resulting jitter performance are illustrated in Figure 30,

Figure 31, and Figure 34. Figure 34 shows the loss characteristic

of various reference channels, and Figure 30 and Figure 31 show

resulting DJ and RJ performance vs. equalizer setting against these

channels.

The two LSBs of Register 0x41, Register 0x81, and Register 0xC1

allow programming of all the equalizers in a port simultane-

ously (see Table 13). The 0x42, 0x82, and 0xC2 registers allow

per-lane programming of the equalizers (see Table 22). Be

aware that writing to the port-level equalizer registers updates

and overwrites per-lane settings.

Table 10. Equalizer Settings

Equalization Boost (dB) EQ Register Setting

0

0

2

1

4

2

6

3

8

4

10

5

12

6

14

7

16

8

18

9

EQ Pin

0

N/A

N/A

N/A

1

N/A

N/A

N/A

N/A

N/A

VCC

VTTI

IP_xx

IN_xx

ESD

ON-CHIP TERMINATION

RP

RTERM

RN

RTERM

EQUALIZER

VTHRESH

LOSS

OF SIG

SIGNAL

DETECT

EQ OUT

VEE

Figure 38. Functional Diagram of the AD8155 Receiver

Rev. 0 | Page 18 of 36