AD8155 查看數據表(PDF) - Analog Devices

零件编号

产品描述 (功能)

比赛名单

AD8155 Datasheet PDF : 36 Pages

| |||

AD8155

LOSS OF SIGNAL (LOS)

The serial control interface allows access to the AD8155 loss of

signal features (LOS is not available in pin control mode). Each

receiver includes a low power, loss-of-signal detector. The loss-

of-signal circuit monitors the received data stream and generates a

system interrupt when the received signal power falls below a

fixed threshold. The threshold is 50 mV p-p diff, referred to the

input pins. The LOS circuit monitors the equalized receive wave-

form and integrates the rms power of the equalized waveform

over a selectable interval of either 2 ns or 10 ns. The detectors are

enabled on a per-port basis with Bit 0 of the RXA/B/C LOS control

registers (0x51, 0x91, 0xD1).

By default, when the receiver detects an LOS event, it squelches

its associated transmitter, lowering the output current to

submicroamps. This prevents the high gain, wide bandwidth

signal path from turning low level system noise on an undriven

input pair into a source of hostile crosstalk at the transmitter.

The squelch feature can be disabled with Bit 3 of the global

squelch control register (0x04).

The LOS_INT pin evaluates a logical OR of all LOS status

register bits for all enabled receivers (LOS status registers are

located at 0x45, 0x85, and 0xC5). The upper two bits in the

RXA, RXB, and RXC LOS status registers are sticky, whereas

the two LSBs are continuously updated to indicate the instantan-

eous status of LOS for an enabled receiver. The sticky bits are

cleared by writing 0 to the RXA, RXB, and RXC LOS status

registers. The LOS_INT pin remains high after an LOS event

until all sticky registers are cleared and all active status registers

(for example, Bits[1:0]) read 0. The LOS_INT pin requires that

an initialization sequence be enabled (see the Applications

Information section).

The LOS_INT pin can be used to generate an interrupt for the

system control software. In a standard implementation, when

LOS_INT goes high, the system software registers the interrupt

and polls the RXA, RXB, and RXC LOS status registers to

determine which input lost signal and whether the signal has

been restored.

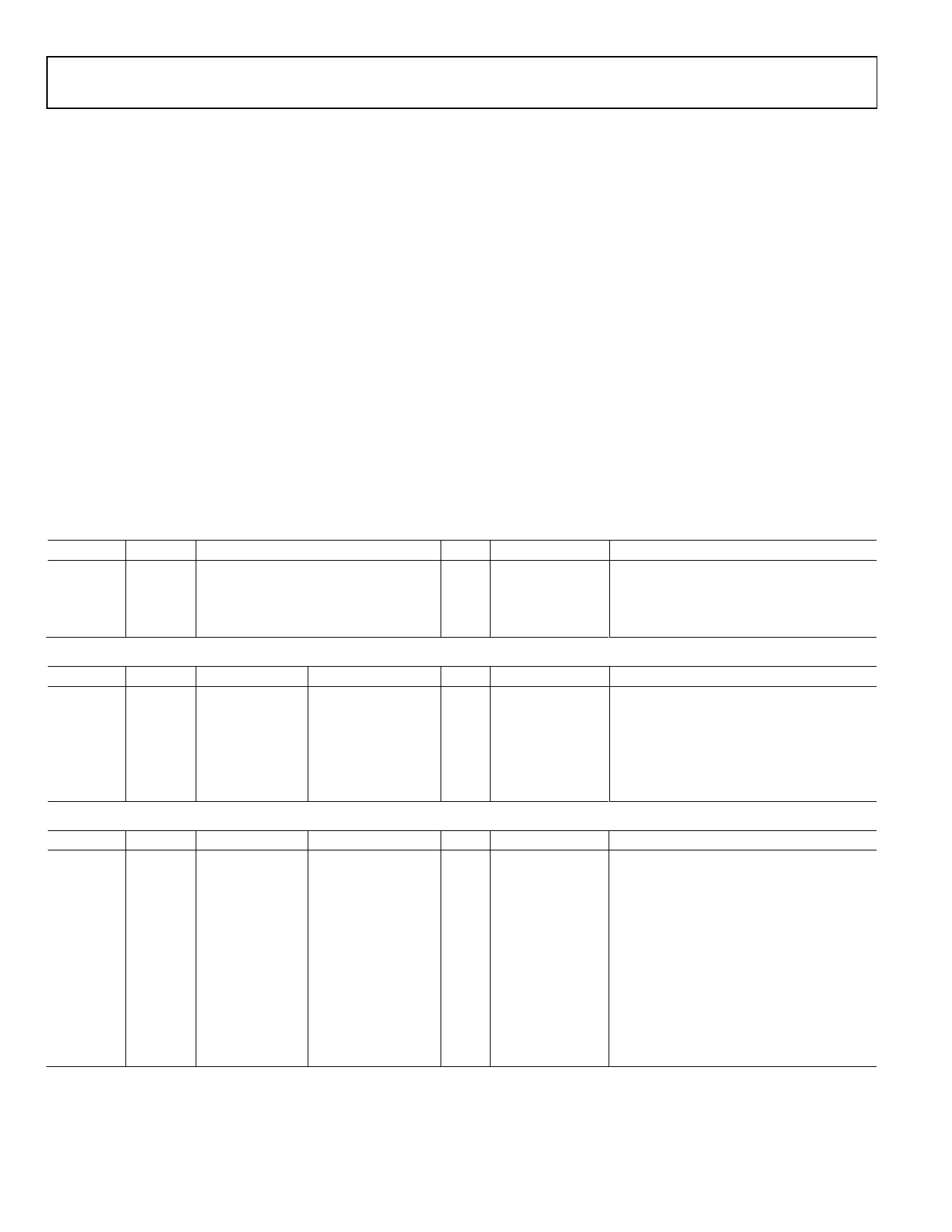

Table 14. Global Loss-of-Signal Squelch Control Register

Address Default Register Name

0x04

0x0F

Global Squelch Ctrl

Table 15. Port-Level Loss-of-Signal Control Registers

Address Port

Default

Register Name

0x51

0x91

Port A

Port B

0x05

0x05

RX[A/B/C] LOS

control

0xD1

Port C 0x05

Table 16. Port-Level Loss-of-Signal Status Registers

Address Port

Default

Register Name

0x45

Port A Read only

0x85

0xC5

Port B

Port C

Write 0 to clear RX[A/B/C] LOS

status

Bit Bit Name

7:4 Reserved

3

GSQLCH_ENB

2:0 Reserved

Functionality Description

Set to 0

0: LOS auto squelch disabled

1: LOS auto squelch enabled

Set to 1

Bit Bit Name

7:3 Reserved

2

LOS_FILT

1

Reserved

0

LOS_ENB

Functionality Description

Set to 0

0: LOS filter time constant = 2 ns

1: LOS filter time constant = 10 ns

Set to 0

0: LOS disabled

1: LOS enabled

Bit Bit Name

Functionality Description

7:6 Reserved

5:4 LOS[A/B/C][1:0] 00: LOS event has not occurred.

sticky

01: LOS event has occurred on Lane 0.

10: LOS event has occurred on Lane 1.

11: LOS event has occurred on both lanes.

Read only; write 0 to clear.

3:2 Reserved

1:0 LOS[A/B/C][1:0] 00: active signals on both lanes.

active

01: inactive signal on Lane 0.

10: inactive signal on Lane 1.

11: inactive signals on both lanes.

Read only.

Rev. 0 | Page 20 of 36