ADG738 查看數據表(PDF) - Analog Devices

零件编号

产品描述 (功能)

比赛名单

ADG738 Datasheet PDF : 20 Pages

| |||

Data Sheet

ADG738/ADG739

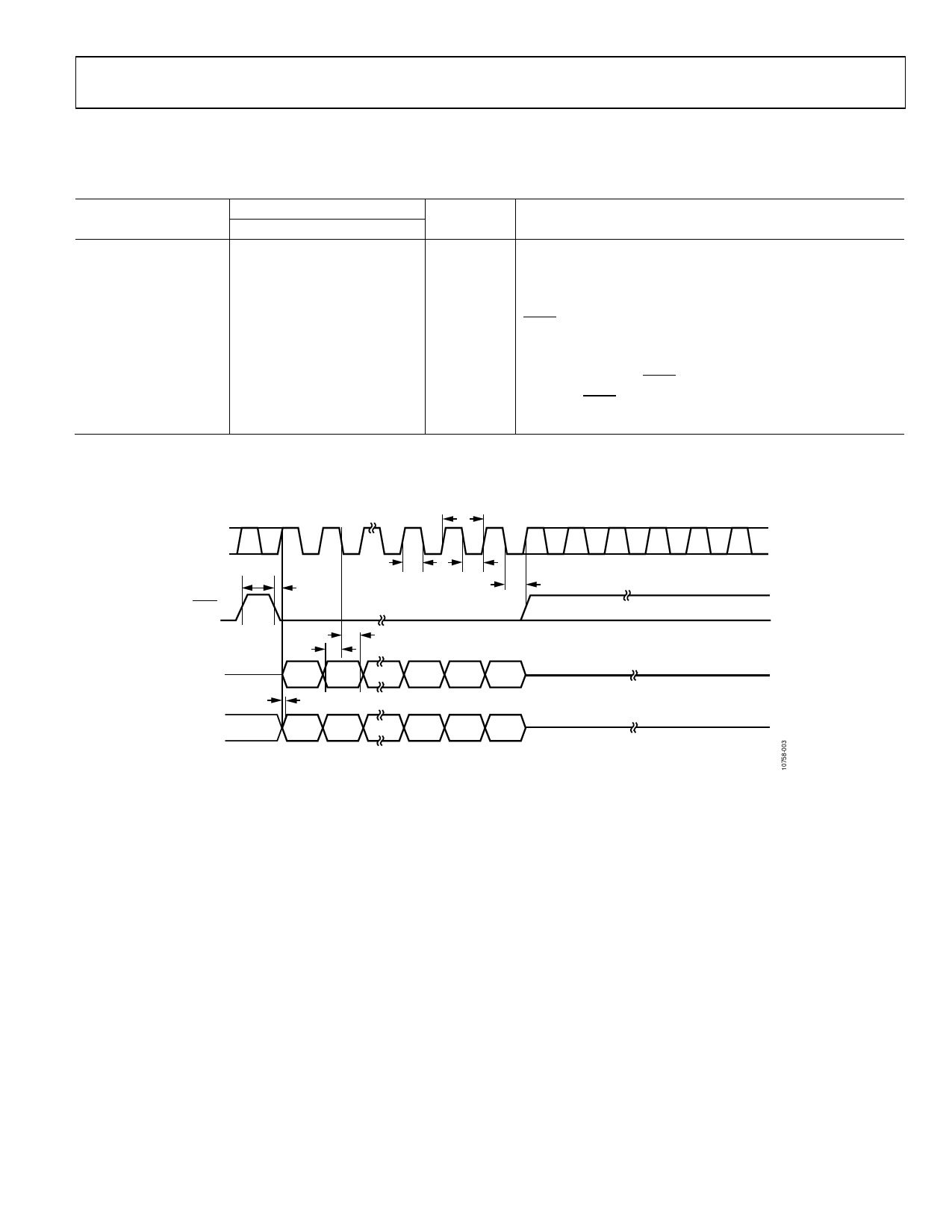

TIMING CHARACTERISTICS

VDD = 2.7 V to 5.5 V. All specifications −40°C to +105°C, unless otherwise noted.

Table 3.

Parameter1, 2

fSCLK

t1

t2

t3

t4

t5

t6

t7

t8

t9 3

Limit at TMIN, TMAX

Min

Max

30

33

13

13

0

5

4.5

0

33

20

Unit

MHz

ns

ns

ns

ns

ns

ns

ns

ns

ns min

Test Conditions/Comments

SCLK cycle frequency

SCLK cycle time

SCLK high time

SCLK low time

SYNC to SCLK active edge setup time

Data setup time

Data hold time

SCLK falling edge to SYNC rising edge

Minimum SYNC high time

SCLK rising edge to DOUT valid

1 See Figure 3.

2 All input signals are specified with tr = tf = 5 ns (10% to 90% of VDD) and timed from a voltage level of (VIL + VIH)/2.

3 CL = 20 pF, RL = 1 kΩ.

SCLK

SYNC

DIN

DOUT

t8

t4

t6

t5

DB7

t9

DB71

t1

t2

t3

t7

DB0

DB01

1DATA FROM LAST WRITE CYCLE.

Figure 3. 3-Wire Serial Interface Timing Diagram

Rev. A | Page 5 of 20