HI5780-EV 查看數據表(PDF) - Intersil

零件编号

产品描述 (功能)

比赛名单

HI5780-EV Datasheet PDF : 8 Pages

| |||

HI5780

Electrical Specifications AVDD, DVDD = 5.00V, VREF = 2.0V, fCLK = 80 MSPS, RLOAD = 200Ω, RREF = 3.3kΩ,

TA = 25oC (Continued)

HI5780JCQ

PARAMETER

TEST CONDITIONS

MIN TYP MAX

DIGITAL INPUTS (D9-D0, CLK, BLK, PD)

Input Logic High Voltage, VIH

Input Logic Low Voltage, VIL

Input Logic Current, IIH

Input Logic Current, IIL

Digital Input Capacitance, CIN

TIMING CHARACTERISTICS

(Note 5)

(Note 5)

(Note 5)

(Note 5)

(Note 3)

2.15

-

-

-

-

0.85

-

-

5

-5

-

-

-

3.0

-

Data Setup Time, tSU

Data Hold Time, tHLD

Propagation Delay Time, tPD

CLK Pulse Width, tPW1, tPW2

POWER SUPPLY CHARACTERISTICS

(See Figure 1, Note 3)

(See Figure 1, Note 3)

(See Figure 1, Note 3)

(See Figure 1, Note 3)

5.0 3.0

-

1.0

0

-

-

8.0

-

6.25

-

-

IVDD

Power Dissipation

(Notes 4, 5)

(Note 5)

-

20

30

-

100 150

Sleep Mode Power Consumption

PD = 1 (Note 4)

-

1.25

-

NOTES:

2. RLOAD is connected to IOUT (pin 24) and RREF is connected to IREF (pin 17).

3. Parameter guaranteed by design or characterization and not production tested.

4. Typical values are test results at TA = 25oC.

5. All devices are 100% tested at 25oC.

UNITS

V

V

µA

µA

pF

ns

ns

ns

ns

mA

mW

mW

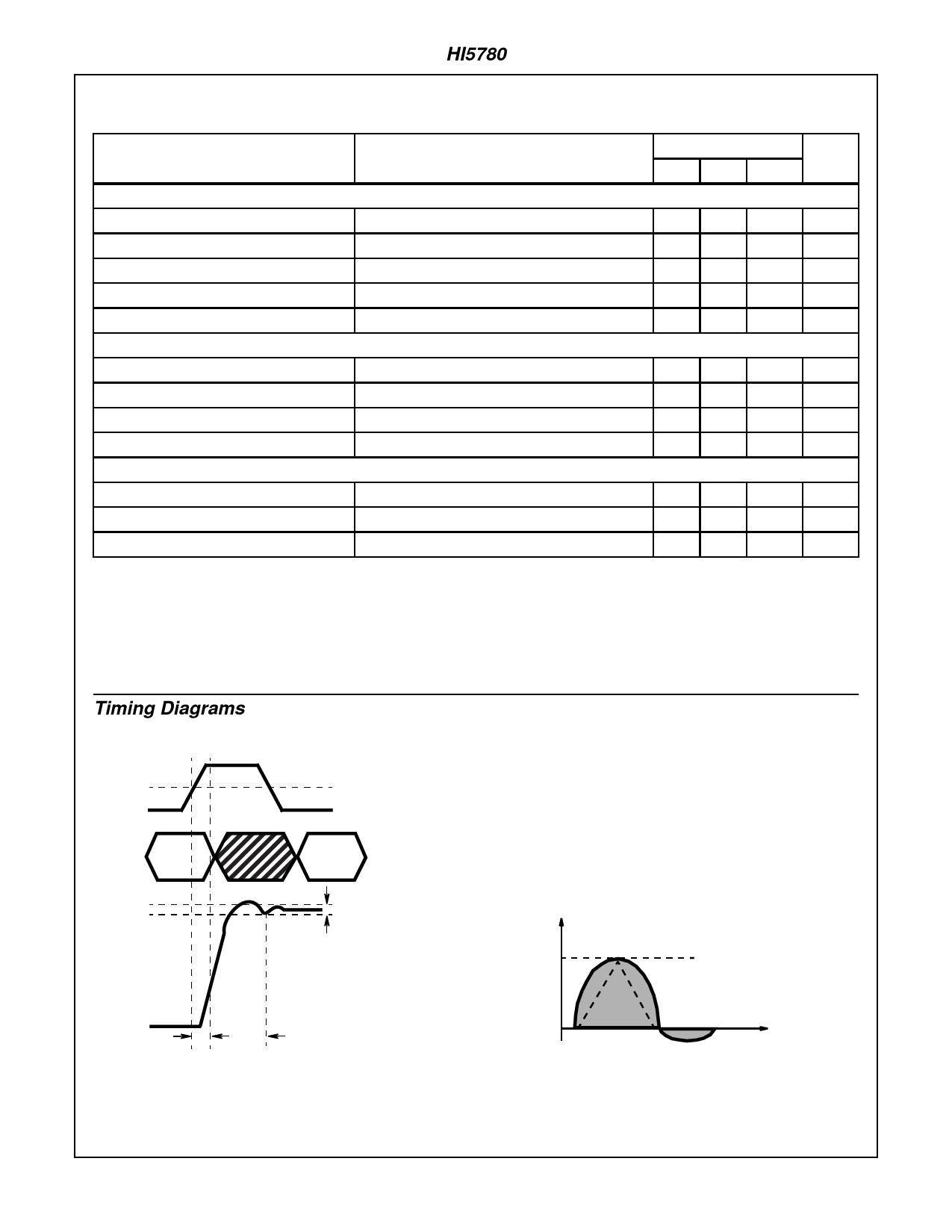

Timing Diagrams

CLK

D9-D0

IOUT

50%

1/2 LSB ERROR BAND

V

GLITCH AREA = 1/2 (H x W)

HEIGHT (H)

tPD

tSETT

FIGURE 1. FULL SCALE SETTLING TIME DIAGRAM

WIDTH (W)

t (ps)

FIGURE 2. PEAK GLITCH AREA (SINGLET) MEASUREMENT

METHOD

10-1719