HSP-EVAL 查看數據表(PDF) - Intersil

零件编号

产品描述 (功能)

比赛名单

HSP-EVAL Datasheet PDF : 12 Pages

| |||

HSP-EVAL

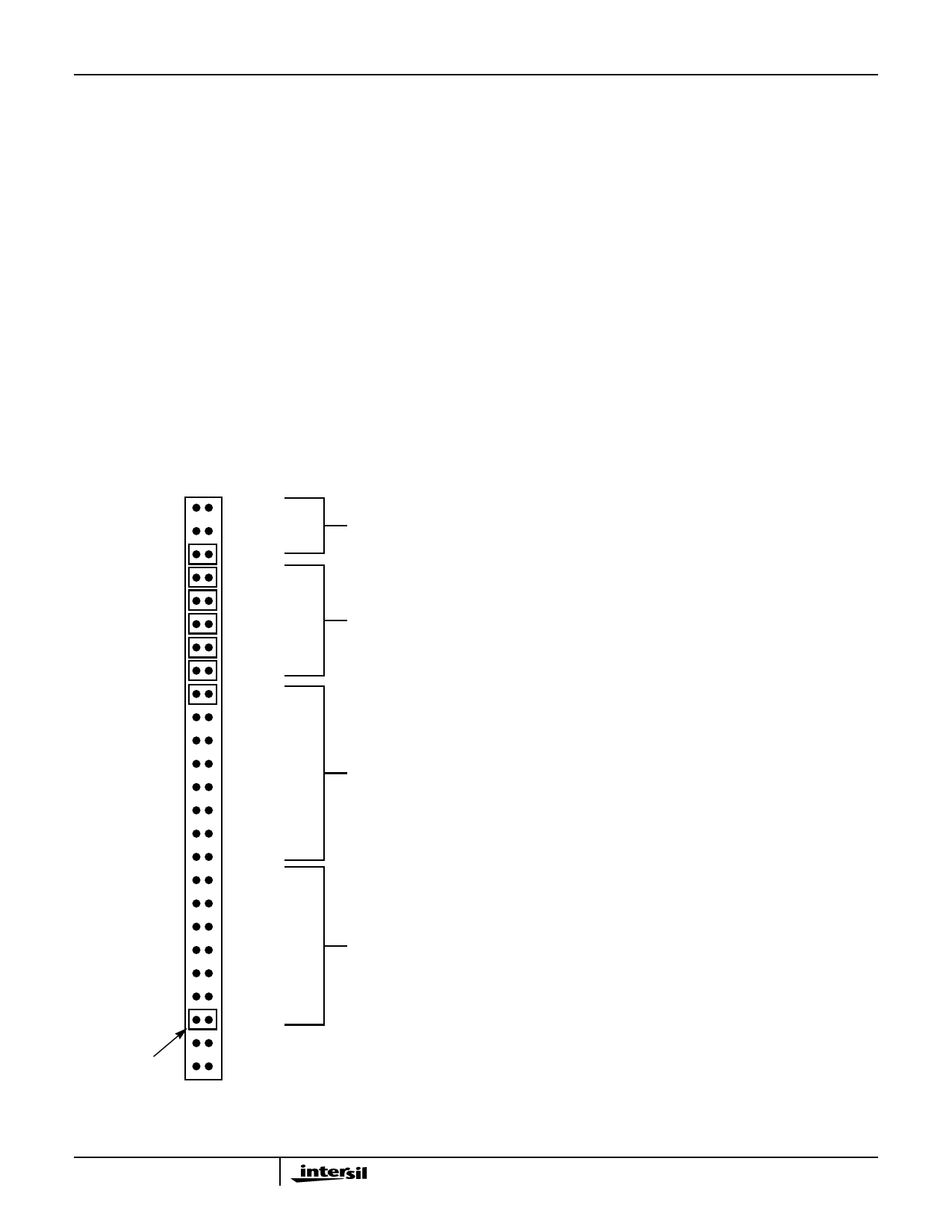

The Clock Select jumpers are used to specify one of the

three available daughter board clocking modes. These

include EXT_CLK for selection of an external clock source,

OSC_CLK for selection of the on board oscillator clock, and

CTL0 for selection of a register driven clock using the LSB of

the CTL Control Register. The clocking modes are described

in the Daughter Board Clocking Modes Section of this

manual. Note: Only one clock source may be jumpered at

a time.

The Output Enable jumpers control the outputs of the

registers driving the four input and control busses (see Bus

and Register Structure Sections). The outputs of the “logical”

Input and Control Registers, Input Registers 1 thru 3 and the

CTL Control Register, are enabled by placing jumpers at the

OE_BUS1, OE_BUS2, OE_BUS3, OECTLLO, and

OECTLHI positions respectively. The two eight bit registers

which make up the CTL Control Register are enabled

separately by using OECTLHI to enable CTL8-15 and

OECTLLO to enable CTL0-7. If a jumper is removed, the

output of the respective register is three-stated.

EXT_CLK

OSC_CLK

CLOCK SELECT

JUMPERS

CTL0

OE_BUS1

OE_BUS2

OE_BUS3

OUTPUT ENABLE

JUMPERS

OECTLLO

OECTLHI

ADDR0

ADDR1

ADDR2

ADDR3

ADDR4

BOARD ADDRESS

JUMPERS

ADDR5

ADDR6

ADDR7

STAT0

STAT1

STAT2

STAT3

PCRD0

OUTPUT SELECT

JUMPERS

PCRD1

SR_RD

DEFAULT

JUMPER

PLACEMENT

INDICATOR

N.C.

N.C.

FIGURE 4. CONFIGURATION JUMPER FIELD J4

The Board Address Jumpers are used to specify the HSP-

EVAL board address used for data transfers via the Parallel

Port Bus. An address from 0 to 7 may be selected by

inserting a jumper in positions ADDR0 thru ADDR7

respectively. Only one jumper may be inserted in this field.

The Output Select jumpers are used to configure the

mapping from the daughter board output and status busses

to the serial output lines of the Parallel Port Bus. The

mapping of the Status Bus to the Parallel Port Bus is

achieved by first selecting the desired Status Bus signal and

then selecting the desired Parallel Port Bus serial output line.

This mapping is achieved by inserting a jumper to select one

of the four status lines, STAT0 thru STAT3, and then

specifying the serial output line by inserting a jumper at

either the PCRD0 or PCRD1 position. Only one of the four

status lines may be selected for output to the Parallel Port

Bus. The output of the 32-bit Shift Register is selected for

output via the PCRD2 line of the Parallel Port Bus by

inserting a jumper in the SR_RD position.

HSP-EVAL Limited Warranty

Intersil warrants the HSP-EVAL to be free of defects in

material and workmanship under normal use for a period of

ninety (90) days. Intersil also warrants that the HSP-EVAL

User's Manual is substantially complete and contains all the

information which Intersil considers necessary to use the

HSP-EVAL, and that the HSP-EVAL functions substantially

as described in the HSP-EVAL User's Manual. Intersil will

replace the HSP-EVAL as Intersil' sole duty under this

warranty only if you ship it, postage prepaid, to Intersil within

90 days of such acquisition and provide proof of date of

acquisition.

This limited warranty does not extend to any products which

have been damaged as a result of accident, misuse, abuse,

or as a result of service or modification by anyone other than

Intersil or Intersil’s' authorized representatives.

Intersil makes no other express or implied warranty with

respect to the HSP-EVAL other than the limited warranty set

forth above. Intersil disclaims all implied warranties of

merchantability and/or fitness for a particular purpose. In any

event, all implied warranties shall be limited to the duration of

this warranty. The liability of Intersil, if any, shall under

any tort, contract or other legal theory be limited to the

actual price paid for such product and shall in no event

include incidental, consequential, special or indirect

damages of any kind, even if Intersil is aware of the

possibility of such damages.

Intersil reserves the right to revise and make changes to this

manual and the HSP-EVAL from time to time without

obligation to notify any person of, or to provide any person

with, such revisions or changes.

8