HY57V641620ELT 查看數據表(PDF) - Hynix Semiconductor

零件编号

产品描述 (功能)

比赛名单

HY57V641620ELT Datasheet PDF : 13 Pages

| |||

64Mb Synchronous DRAM based on 1M x 4Bank x16 I/O

Document Title

4Bank x 1M x 16bits Synchronous DRAM

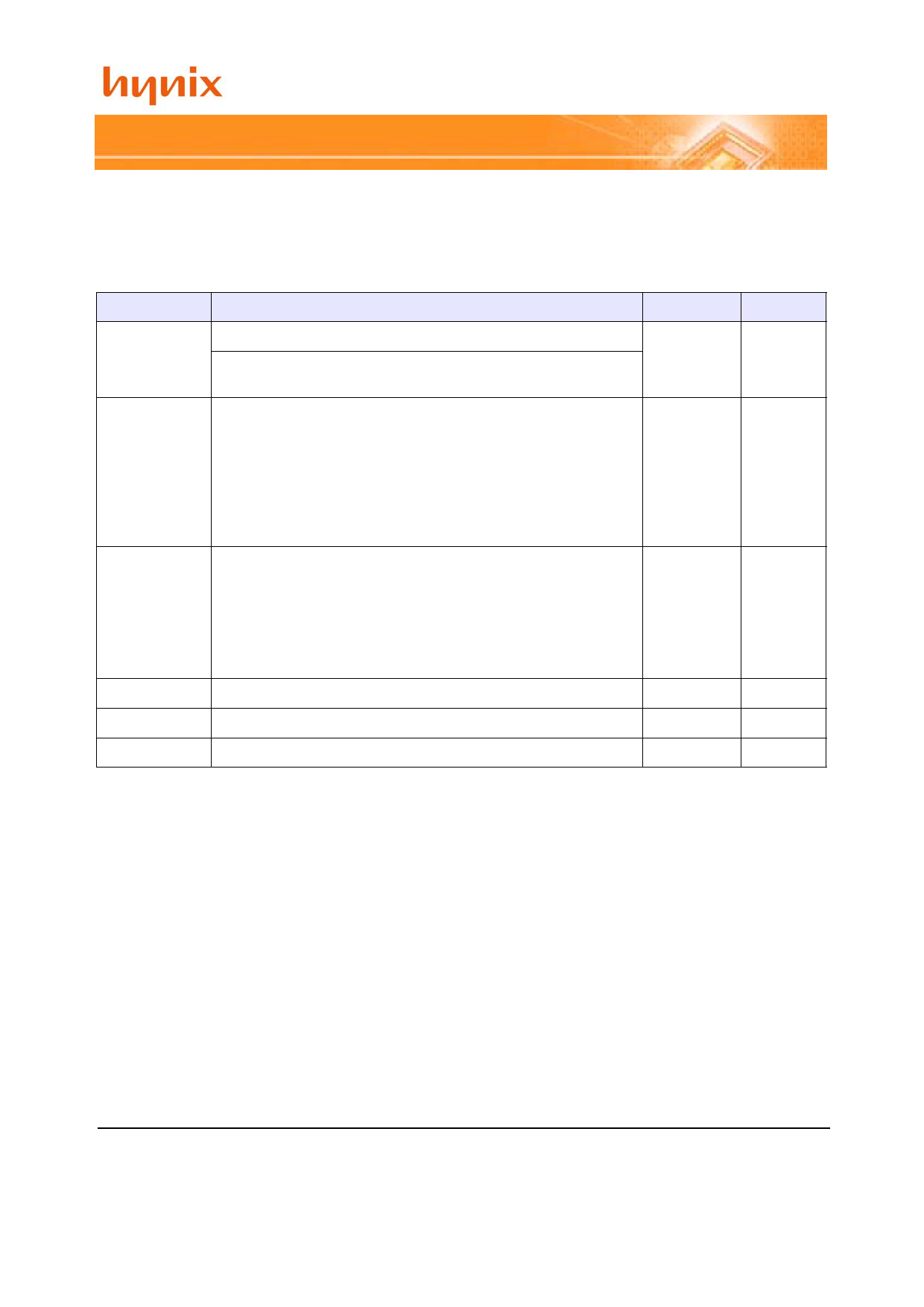

Revision History

Revision No.

History

First Version Release

1.0

1. Changed tOH: 2.0 --> 2.5

[tCK = 7 & 7.5 (CL3) Product]

1. Changed Input High/Low Voltage (Page 08)

2. Changed DC characteristics (Page 09)

- IDD2NS: 18mA -> 15mA

1.1

- IDD5:210 / 195 / 180mA -> 170 / 160 / 150mA

[Speed 200 / 166 / 143 / 133MHz]

3. Changed Clock High / Low pulse width Time (Page 11)

4. Changed tAC Time (Page11)

5. Changed tRRD Time (Page12)

1. Corrected Revision No.: 2.0 -> 1.1

2. Deleted Remark at Revision History

3. Corrected AC OPERATING CONDITION

1.2

- CL 50pF -> 30pF

4. Changed DC OPERATING CONDITION

- VIH MAX VDDQ+2.0 -> VDDQ+0.3 and Typ 3.3 -> 3.0

- VIL MIN VSSQ-2.0 -> -0.3

1.3

1. Modified note for Super Low Power in ORDERING INFORMATION

1.4

1. Corrected PIN ASSIGNMENT A12 to NC

1.5

1. Corrected comments for overshoot and undershoot

Draft Date

Nov. 2004

Dec. 2004

Dec. 2004

Jan. 2005

Jan. 2005

Feb. 2005

Remark

This document is a general product description and is subject to change without notice. Hynix does not assume any responsibility for

use of circuits described. No patent licenses are implied.

Rev. 1.5 / Feb. 2005

1