M38C88EA-XXXFP 查看數據表(PDF) - MITSUBISHI ELECTRIC

零件编号

产品描述 (功能)

比赛名单

M38C88EA-XXXFP Datasheet PDF : 51 Pages

| |||

PRELIMINARY NSocothimcaene:gpTeah.riasmisetnrioct laimfiintsalasrepescuibfijceacttioton.

MITSUBISHI MICROCOMPUTERS

38C8 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

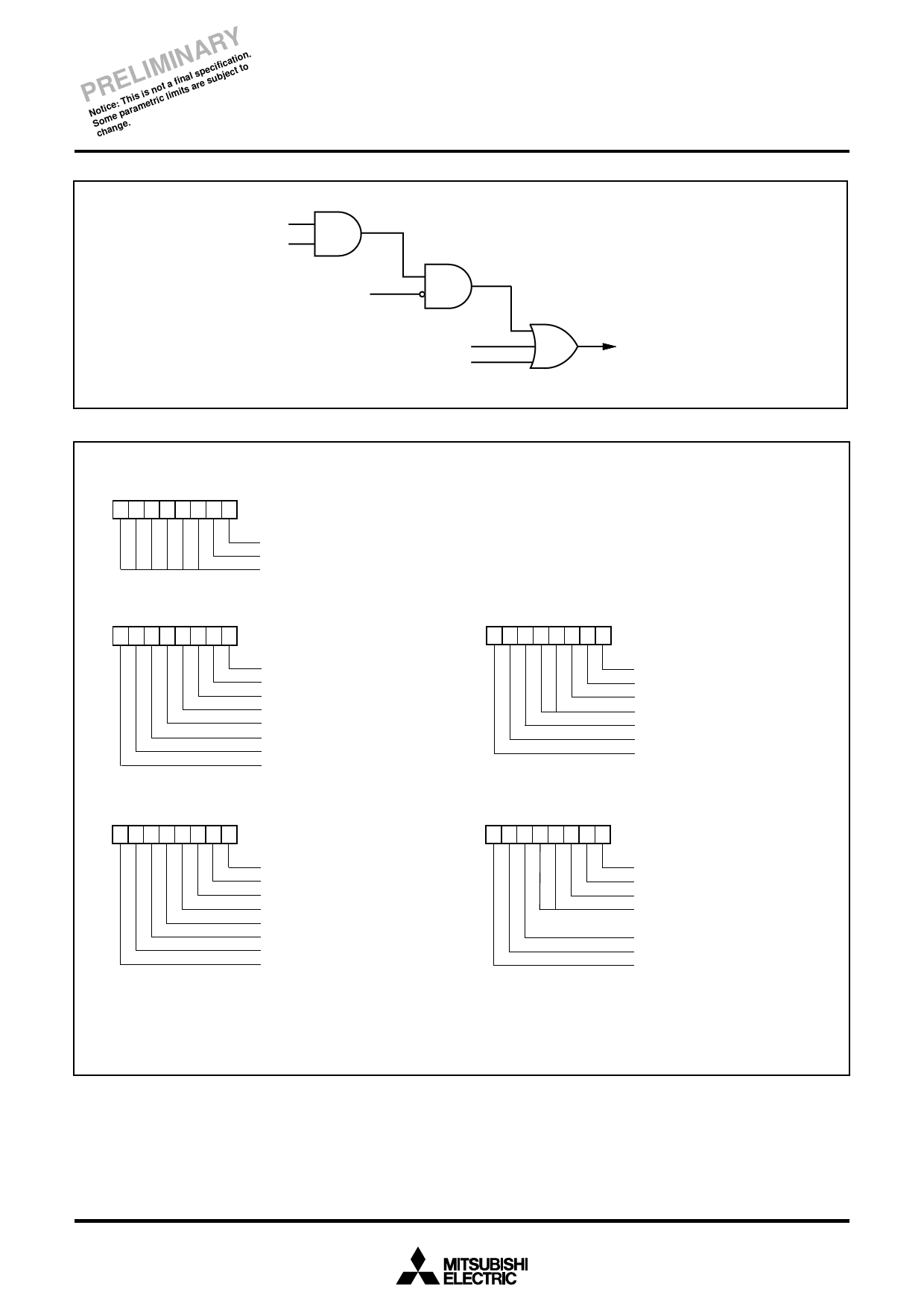

Interrupt request bit

Interrupt enable bit

Interrupt disable flag (I)

BRK instruction

Reset

Fig. 13 Interrupt control

Interrupt request

b7

b0

Interrupt edge selection register

(INTEDGE : address 003A16)

INT0 interrupt edge selection bit

INT1 interrupt edge selection bit 0 : Falling edge active

Not used (return “0” when read) 1 : Rising edge active

b7

b0

Interrupt request register 1

(IREQ1 : address 003C16)

b7

b0

Interrupt request register 2

(IREQ2 : address 003D16)

INT0 interrupt request bit

INT1 interrupt request bit

Serial I/O receive interrupt request bit

Serial I/O transmit interrupt request bit

Timer X interrupt request bit

Timer Y interrupt request bit

Timer 2 interrupt request bit

Timer 3 interrupt request bit

CNTR0 interrupt request bit

CNTR1 interrupt request bit

Timer 1 interrupt request bit

Not used (returns “0” when read)

Key input interrupt request bit

AD conversion interrupt request bit

Not used (returns “0” when read)

0 : No interrupt request issued

1 : Interrupt request issued

b7

b0

Interrupt control register 1

(ICON1 : address 003E16)

b7

b0

Interrupt control register 2

(ICON2 : address 003F16)

INT0 interrupt enable bit

INT1 interrupt enable bit

Serial I/O receive interrupt enable bit

Serial I/O transmit interrupt enable bit

Timer X interrupt enable bit

Timer Y interrupt enable bit

Timer 2 interrupt enable bit

Timer 3 interrupt enable bit

CNTR0 interrupt enable bit

CNTR1 interrupt enable bit

Timer 1 interrupt enable bit

Not used (returns “0” when read)

(Do not write “1” to this bit)

Key input interrupt enable bit

AD conversion interrupt enable bit

Not used (returns “0” when read)

(Do not write “1” to this bit)

0 : Interrupts disabled

1 : Interrupts enabled

Fig. 14 Structure of interrupt-related registers

18