ADG728 查看數據表(PDF) - Analog Devices

零件编号

产品描述 (功能)

比赛名单

ADG728 Datasheet PDF : 13 Pages

| |||

ADG728/ADG729

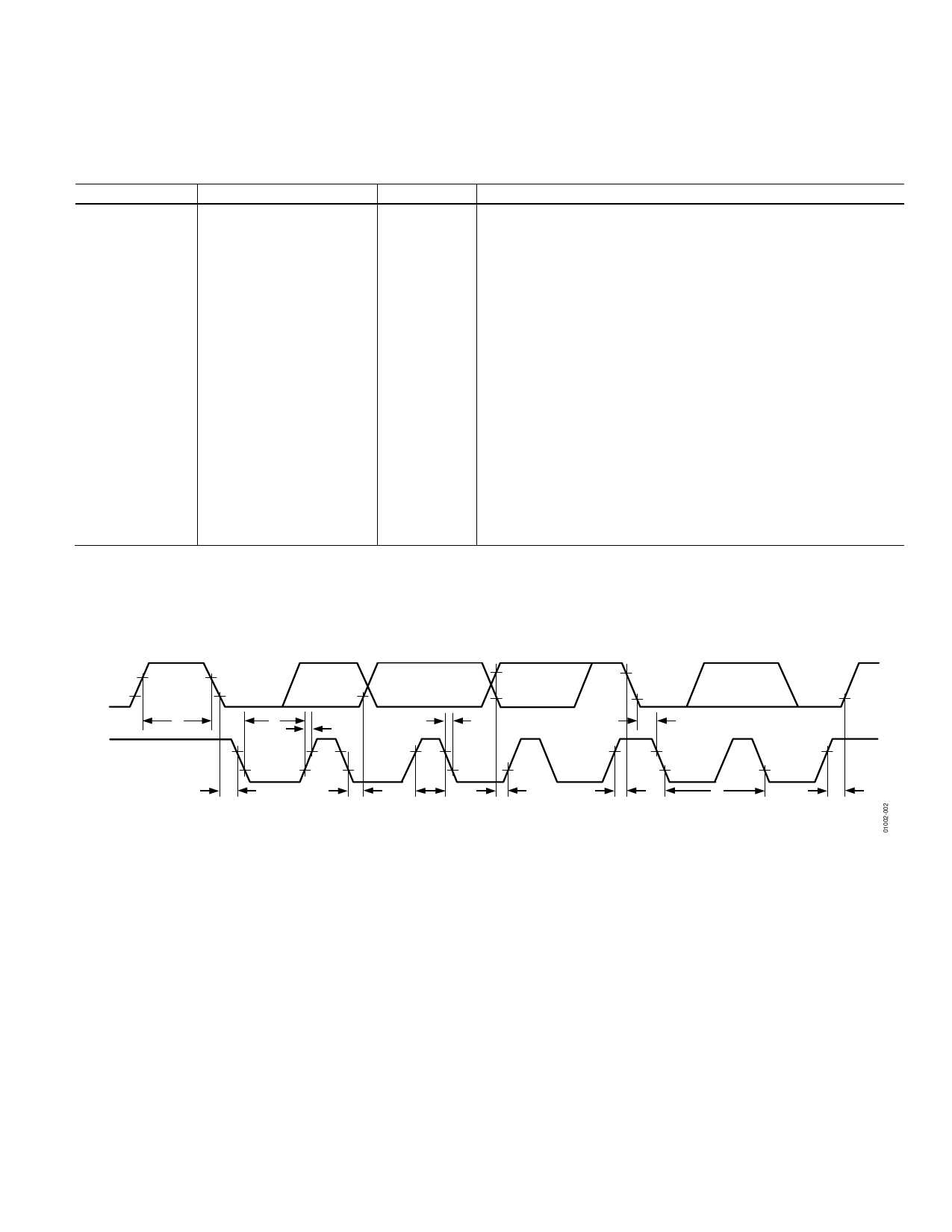

TIMING CHARACTERISTICS

VDD = 2.7 V to 5.5 V. All specifications −40°C to +85°C, unless otherwise noted. See Figure 1.

Parameter

fSCL

t1

t2

t3

t4

t5

t6 1

t7

t8

t9

t10

t11

Cb2

tSP3

Limit at TMIN, TMAX

400

2.5

0.6

1.3

0.6

100

0.9

0

0.6

0.6

1.3

300

20 + 0.1Cb2

250

300

0.1Cb2

400

50

Unit

kHz max

µs min

µs min

µs min

µs min

ns min

µs max

µs min

µs min

µs min

µs min

ns max

ns min

ns max

ns max

ns min

pF max

ns max

Test Conditions/Comments

SCL clock frequency

SCL cycle time

SCL high time, tHIGH

SCL low time, tLOW

Start/repeated start condition hold time, tHD, STA

Data setup time, tSU, DAT

Data hold time, tHD, DAT

Setup time for repeated start, tSU, STA

Stop condition setup time, tSU, STO

Bus free time between a stop condition and a start condition, tBUF

Rise time of both SCL and SDA when receiving, tR

Fall time of SDA when receiving, tF

Fall time of SDA when transmitting, tF

Capacitive load for each bus line

Pulse width of spike suppressed

1 A master device must provide a hold time of at least 300 ns for the SDA signal (referred to the VIH min of the SCL signal) to bridge the undefined region of the falling

edge of SCL.

2 Cb is the total capacitance of one bus line in pF. tR and tF measured between 0.3 VDD and 0.7 VDD.

3 Input filtering on both the SCL and SDA inputs suppress noise spikes that are less than 50 ns.

SDA

t9

t3

t10

t11

t4

SCL

t4

START

CONDITION

t6

t2

t5

START

CONDITION

t7

t1

REPEATED

START

CONDITION

Figure 1. 2-Wire Serial Interface Timing Diagram

t8

STOP

CONDITION

–4–

REV. C