AD9430BSVZ-170 查看數據表(PDF) - Analog Devices

零件编号

产品描述 (功能)

比赛名单

AD9430BSVZ-170 Datasheet PDF : 44 Pages

| |||

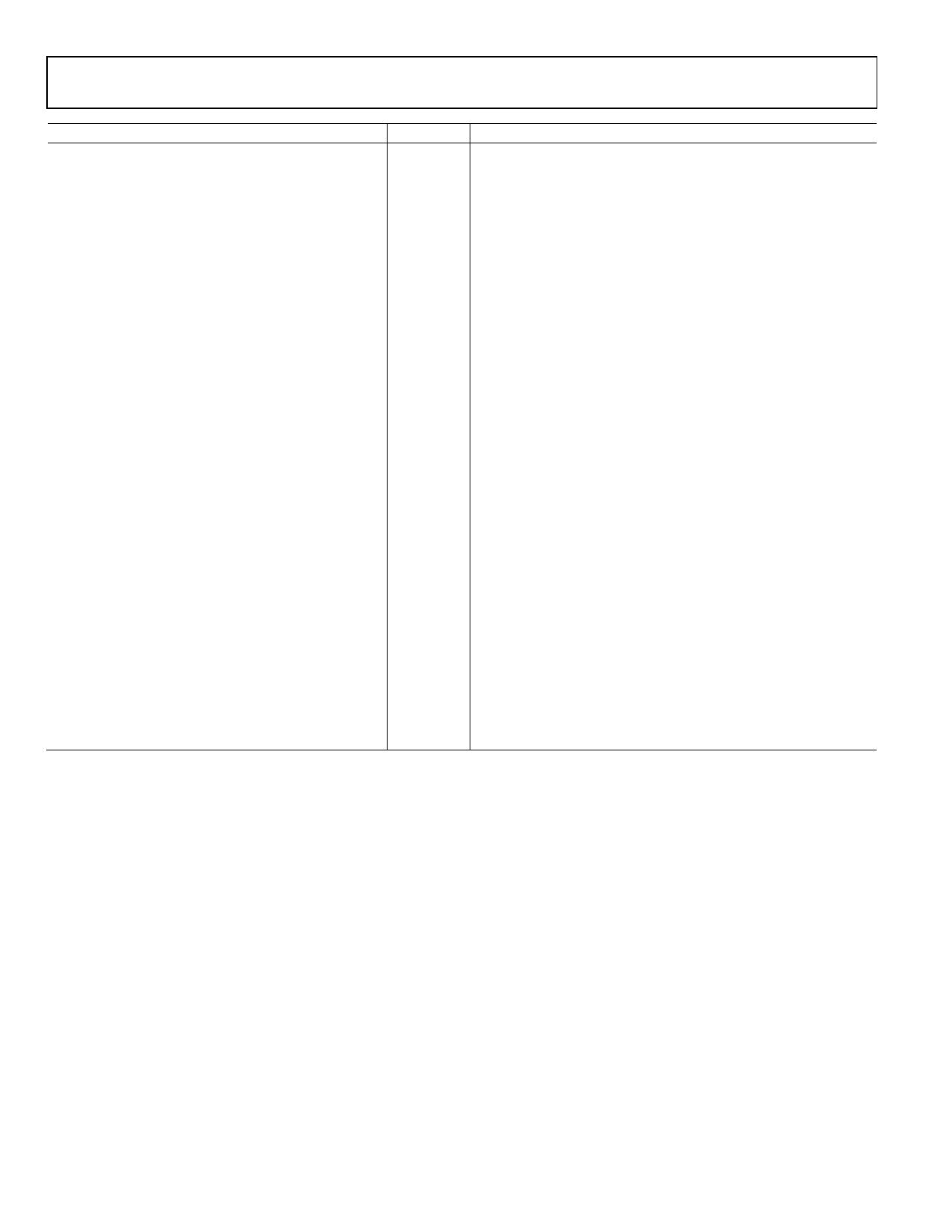

AD9430

Pin Number

36

37

44

45

46

47, 54, 62, 75, 83

48, 53, 61, 67, 74, 82

49

50

51

52

55

56

57

58

59

60

63

64

69

70

71

72

73

76

77

78

79

80

81

84

85

Mnemonic

CLK+

CLK–

DB0

DB1

DB2

DRVDD

DRGND1

DB3

DB4

DB5

DB6

DB7

DB8

DB9

DB10

DB11

OR_B

DCO–

DCO+

DA0

DA1

DA2

DA3

DA4

DA5

DA6

DA7

DA8

DA9

DA10

DA11

OR_A

Description

Clock Input—True.

Clock Input—Complement.

B Port Output Data Bit (LSB).

B Port Output Data Bit.

B Port Output Data Bit.

3.3 V Digital Output Supply (3.0 V to 3.6 V).

Digital Output Ground.

B Port Output Data Bit.

B Port Output Data Bit.

B Port Output Data Bit.

B Port Output Data Bit.

B Port Output Data Bit.

B Port Output Data Bit.

B Port Output Data Bit.

B Port Output Data Bit.

B Port Output Data Bit (MSB).

B Port Overrange.

Data Clock Output—Complement.

Data Clock Output—True.

A Port Output Data Bit (LSB).

A Port Output Data Bit.

A Port Output Data Bit.

A Port Output Data Bit.

A Port Output Data Bit.

A Port Output Data Bit.

A Port Output Data Bit.

A Port Output Data Bit.

A Port Output Data Bit.

A Port Output Data Bit.

A Port Output Data Bit.

A Port Output Data Bit (MSB).

A Port Overrange.

1 AGND and DRGND should be tied together to a common ground plane.

2 DS Complement (DS−); can be tied to AVDD (as recommended) or left floating with no ill effects.

Rev. E | Page 12 of 44