W40S11-02H 查看數據表(PDF) - SpectraLinear Inc

零件编号

产品描述 (功能)

比赛名单

W40S11-02H Datasheet PDF : 9 Pages

| |||

W40S11-02

Signaling Requirements

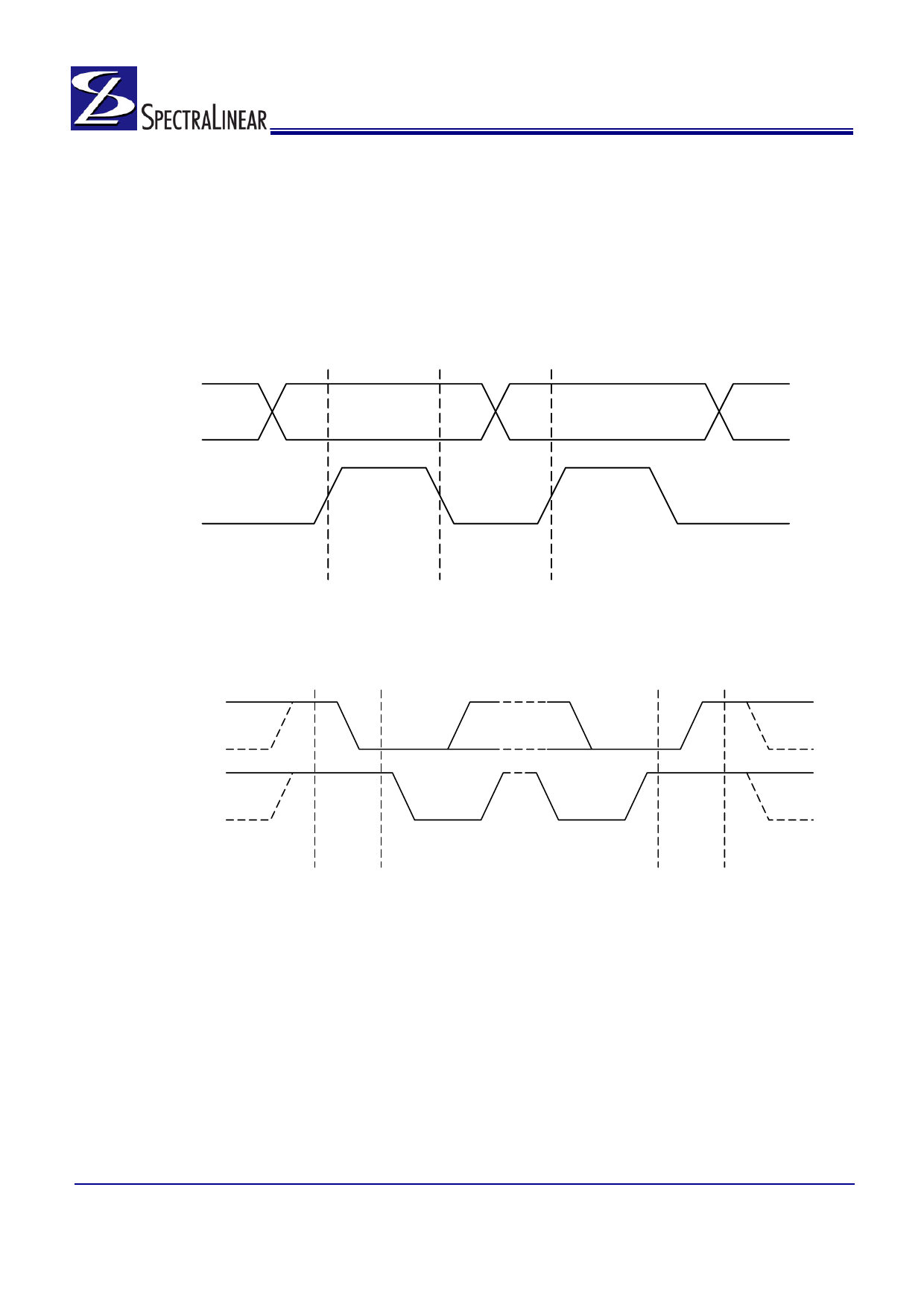

As shown in Figure 2, valid data bits are defined as stable logic

0 or 1 condition on the data line during a clock HIGH (logic 1)

pulse. A transitioning data line during a clock HIGH pulse may

be interpreted as a start or stop pulse (it will be interpreted as

a start or stop pulse if the start/stop timing parameters are

met).

A write sequence is initiated by a “start bit” as shown in Figure

1. A “stop bit” signifies that a transmission has ended.

As stated previously, the W40S11-02 sends an “acknowledge”

pulse after receiving eight data bits in each byte as shown in

Figure 2.

Sending Data to the W40S11-02

The device accepts data once it has detected a valid start bit

and address byte sequence. Device functionality is changed

upon the receipt of each data bit (registers are not double

buffered). Partial transmission is allowed meaning that a trans-

mission can be truncated as soon as the desired data bits are

transmitted (remaining registers will be unmodified). Trans-

mission is truncated with either a stop bit or new start bit

(restart condition).

SDATA

SCLOCK

Valid

Data

Bit

Change

of Data Allowed

Figure 2. Serial Data Bus Valid Data Bit

SDATA

SCLOCK

Start

Bit

Stop

Bit

Figure 1. Serial Data Bus Start and Stop Bit

Rev 1.0, Dec. 01, 2006

Page 5 of 9