MU9C8328A-RDC 查看數據表(PDF) - MUSIC Semiconductors

零件编号

产品描述 (功能)

比赛名单

MU9C8328A-RDC Datasheet PDF : 16 Pages

| |||

MU9C8328A Ethernet Interface

APPLICATIONS Continued

the Persistent destination to the Comparand register as

shown in Table 3. If only one LANCAM is used, Table 3

would be modified to replace steps 9 through 14 with a

TCO DS (0228H) followed by a 0000H.

Enabling Network Activity

After the LANCAMs have been initialized, the MU9C8328A

is enabled to begin processing network traffic by setting

bit 13 (NETEN) in its Control register to a 1 along with the

desired filtering actions and interrupt enables.

Responding to Interrupts

Depending on the filtering or error interrupt conditions set

in the MU9C8328A Control register, the /INT line will assert

at the end of the frame SA field. The host can then read the

MU9C8328A Status register to determine the cause of the

interrupt, whereupon the Status register is reset. If there

was a DA match interrupt and read associated data was

set, then the associated data segment stored in the

LANCAM at the same location that matched the frame’s

DA can be read out of the Associated Data register (03H).

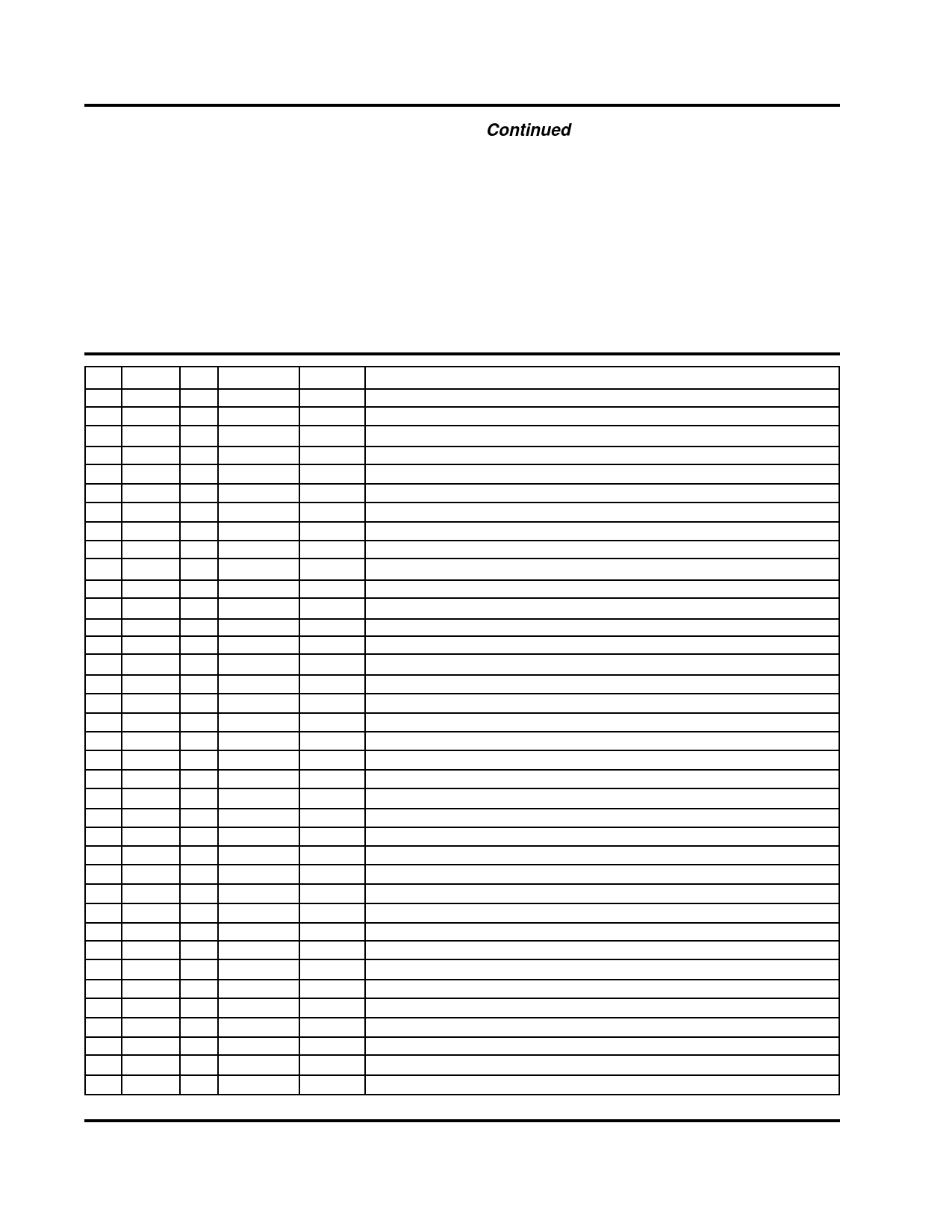

Step A(2–0)

1 0H

2 5H

3 5H

4 5H

5 5H

6 5H

7 5H

8 5H

9 5H

10 5H

11 5H

12 5H

13 5H

14 5H

15 5H

16 5H

17 5H

18 5H

19 5H

20 5H

21 7H

22 5H

23 5H

24 5H

25 5H

26 5H

27 5H

28 5H

29 7H

30 7H

31 7H

32 7H

33 5H

34 5H

35 5H

36 5H

37 0H

/WE Mnemonic D(15–0)

L

C000H

H

0000H

L TCO_DS 0228H

L

FFFFH

L TCO_CT 0200H

L

0000H

L TCO_PA 0208H

L

0000H

L

SFF

0700H

L TCO_PA 0208H

L

0001H

L

SFF

0700H

L TCO_CT 0200H

L

0000H

L

SBR

0619H

L TCO_CT 0200H

L

8111H

L TCO_SC 0210H

L

0000H

L SPD_MR1 0108H

L

FFF0H

L SPD_CR 0100H

L

SFR

0618H

L TCO_CT 0200H

L

8041H

L SPD_MR1 0108H

L TCO_SC 0210H

L

1C04H

L

FFF0H

L

FFFFH

L

FFFFH

L

FFFFH

L SPD_CR 0100H

L TCO_SC 0210H

L

3808H

L SPS_HM 0005H

L

290BH

Comments

Pass all frames during initialization

Command Read to reset LANCAM state machines

Selects all Device Select registers

Selects all LANCAMs

Selects all Control registers

Resets all memory locations

Selects first Page Address register

Writes first Page Address value

Sets Full flag on first LANCAM

Selects second Page Address register

Writes second Page Address value

Sets Full flag on second LANCAM

Selects all Control registers

Resets all Full flags

Select Background Register set

TCO CT

48RAM, 16CAM, MR1, Enhanced mode

Select Segment Control register

Set Read and Write to segment 0

Set Persistent Destination to Mask Register 1

Setup Time Stamp in lowest 8 bits of segment 0

Set Persistent Destination to Comparand register

Select Foreground Register set

Select Command register

48CAM, 16RAM, No Mask, Enhanced mode

Set Persistent Destination to Mask Register 1

Select Segment Control register

Set to write Segments 0, 1, 2, and 3

Write to Segment 0 of MR1

Write to Segment 1 of MR1

Write to Segment 2 of MR1

Write to Segment 3 of MR1

Set Persistent Destination to Comparand register

Select Segment Control register

Write Segments 1–3, Read Segment 0

Set Persistent source to Highest match

Enable filter, Negative filter on DA, enable learn

Table 3: LANCAM Initialization Code

Rev. 0.8 Draft

10