WM8734 查看數據表(PDF) - Cirrus Logic

零件编号

产品描述 (功能)

比赛名单

WM8734 Datasheet PDF : 45 Pages

| |||

WM8734

Production Data

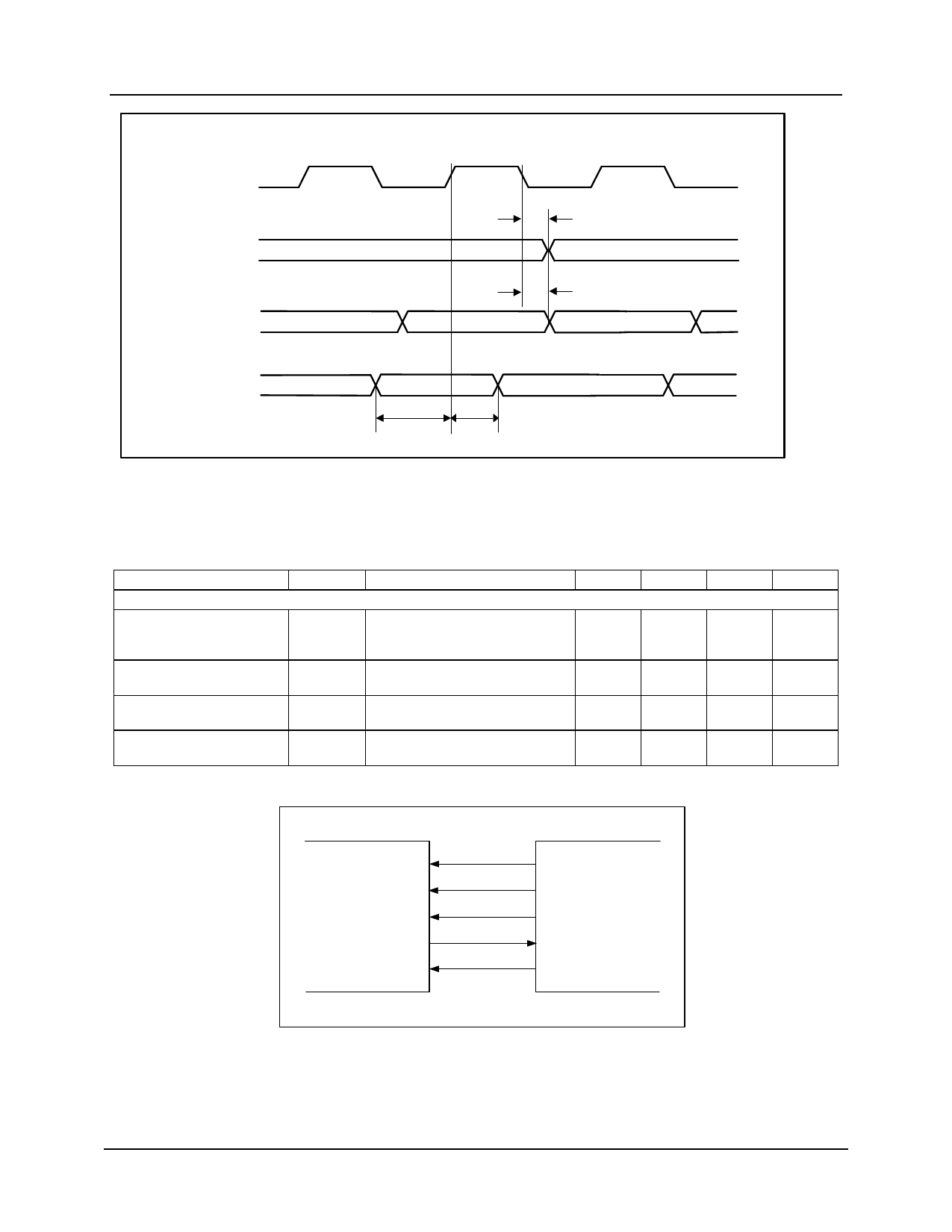

BCLK

(Output)

ADCLRC

DAC/LRC

(Outputs)

ADCDAT

t

DL

tDDA

DACDAT

t DST

t DHT

Figure 3 Digital Audio Data Timing – Master Mode

Test Conditions

AVDD, DBVDD = 3.3V, AGND = 0V, DCVDD = 3.3V, DGND = 0V, TA = +25oC, Slave Mode, fs = 48kHz, MCLK = 256fs unless

otherwise stated.

PARAMETER

SYMBOL

Audio Data Input Timing Information

ADCLRC/DACLRC

tDL

propagation delay from

BCLK falling edge

ADCDAT propagation delay

tDDA

from BCLK falling edge

DACDAT setup time to

tDST

BCLCK rising edge

DACDAT hold time from

tDHT

BCLK rising edge

TEST CONDITIONS

MIN

TYP

MAX

UNIT

0

10

ns

0

15

ns

10

ns

10

ns

DIGITAL AUDIO INTERFACE – SLAVE MODE

BCLK

ADCLRC

WM8734

CODEC

DACLRC

ADCDAT

DACDAT

DSP

ENCODER/

DECODER

Figure 4 Slave Mode Connection

w

PD, Rev 4.4, August 2013

10