81487EIB 查看數據表(PDF) - Renesas Electronics

零件编号

产品描述 (功能)

比赛名单

81487EIB Datasheet PDF : 14 Pages

| |||

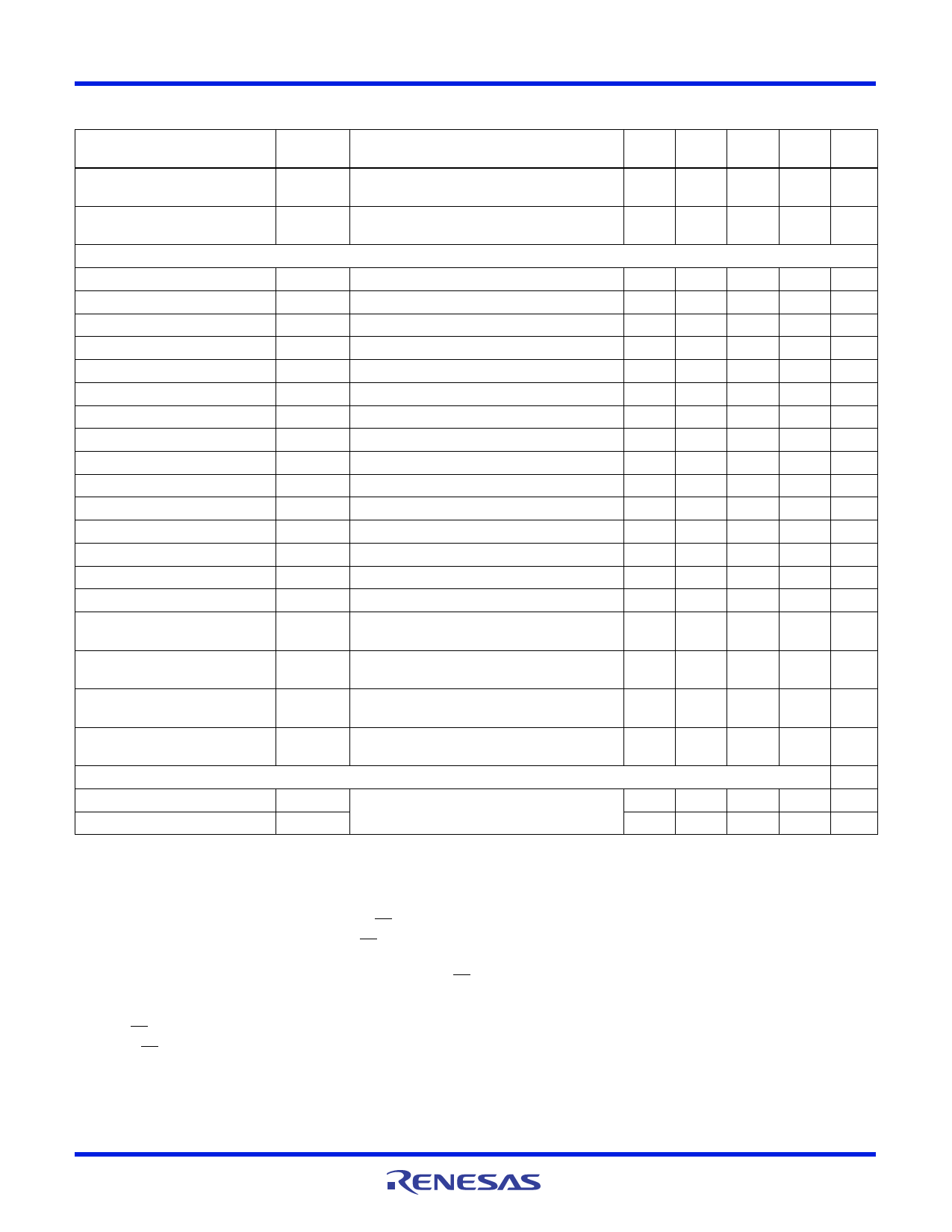

ISL8487E, ISL81487L, ISL81487E

Electrical Specifications Test Conditions: VCC = 4.5V to 5.5V; Unless Otherwise Specified.

Typicals are at VCC = 5V, TA = 25°C, (Note 2) (Continued)

PARAMETER

SYMBOL

TEST CONDITIONS

TEMP

(°C) MIN

TYP MAX UNITS

Receiver Enable from Shutdown to tZH(SHDN) CL = 15pF, SW = GND, (Figure 5, Notes 7, 9)

Full

-

800 2500 ns

Output High

Receiver Enable from Shutdown to tZL(SHDN) CL = 15pF, SW = VCC, (Figure 5, Notes 7, 9)

Full

-

800 2500 ns

Output Low

SWITCHING CHARACTERISTICS (ISL81487L)

Driver Input to Output Delay

tPLH, tPHL RDIFF = 54, CL = 100pF, (Figure 2)

Full

150

650 1200

ns

Driver Output Skew

tSKEW RDIFF = 54, CL = 100pF, (Figure 2)

Full

-

160

600

ns

Driver Differential Rise or Fall Time tR, tF RDIFF = 54, CL = 100pF, (Figure 2)

Full

250

900 1200

ns

Driver Enable to Output High

tZH

CL = 100pF, SW = GND, (Figure 3, Note 5)

Full

100 1000 1500 ns

Driver Enable to Output Low

tZL

CL = 100pF, SW = VCC, (Figure 3, Note 5)

Full

100 1000 1500

ns

Driver Disable from Output High

tHZ

CL = 15pF, SW = GND, (Figure 3)

Full

150

750 1500

ns

Driver Disable from Output Low

tLZ

CL = 15pF, SW = VCC, (Figure 3)

Full

150

750 1500

ns

Receiver Input to Output Delay

tPLH, tPHL (Figure 4)

Full

30

175

250

ns

Receiver Skew | tPLH - tPHL |

tSKD (Figure 4)

25

-

13

-

ns

Receiver Enable to Output High

tZH

CL = 15pF, SW = GND, (Figure 5, Note 6)

Full

-

10

50

ns

Receiver Enable to Output Low

tZL

CL = 15pF, SW = VCC, (Figure 5, Note 6)

Full

-

10

50

ns

Receiver Disable from Output High

tHZ

CL = 15pF, SW = GND, (Figure 5)

Full

-

10

50

ns

Receiver Disable from Output Low

tLZ

CL = 15pF, SW = VCC, (Figure 5)

Full

-

10

50

ns

Maximum Data Rate

fMAX

Full

250

-

-

kbps

Time to Shutdown

tSHDN (Note 7)

Full

50

140

600

ns

Driver Enable from Shutdown to

tZH(SHDN) CL = 100pF, SW = GND, (Figure 3, Notes 7, 8)

Full

Output High

-

1100 2000 ns

Driver Enable from Shutdown to

tZL(SHDN) CL = 100pF, SW = VCC, (Figure 3, Notes 7, 8)

Full

Output Low

-

1000 2000 ns

Receiver Enable from Shutdown to tZH(SHDN) CL = 15pF, SW = GND, (Figure 5, Notes 7, 9)

Full

-

900 2000 ns

Output High

Receiver Enable from Shutdown to tZL(SHDN) CL = 15pF, SW = VCC, (Figure 5, Notes 7, 9)

Full

-

900 2000 ns

Output Low

ESD PERFORMANCE

RS-485 Pins (A/Y, B/Z)

Human Body Model

25

-

15

-

kV

All Other Pins

25

-

>7

-

kV

NOTES:

2. Currents into device pins are positive; currents out of device pins are negative. Voltages are referenced to ground unless otherwise specified.

3. Supply current specification is valid for loaded drivers when DE = 0V.

4. Applies to peak current. See “Typical Performance Curves” for more information.

5. When testing the ISL8487E and ISL81487L, keep RE = 0 to prevent the device from entering SHDN.

6. When testing the ISL8487E and ISL81487L, the RE signal high time must be short enough (typically <200ns) to prevent the device from entering

SHDN.

7. The ISL8487E and ISL81487L are put into shutdown by bringing RE high and DE low. If the inputs are in this state for less than 50ns, the parts

are guaranteed not to enter shutdown. If the inputs are in this state for at least 600ns, the parts are guaranteed to have entered shutdown. See

“Low-Power Shutdown Mode” section.

8. Keep RE = VCC, and set the DE signal low time >600ns to ensure that the device enters SHDN.

9. Set the RE signal high time >600ns to ensure that the device enters SHDN.

10. Devices meeting these limits are denoted as “1/8 unit load (1/8 UL)” transceivers. The RS-485 standard allows up to 32 Unit Loads on the bus,

so there can be 256 1/8 UL devices on a bus.

FN6051 Rev.7.00

February 27, 2006

Page 6 of 14